MICRO-TECH PUBLICATIONS

MICRO-TECH PUBLICATIONS P.O. Box 50688, Dubai (U.A.E.)

### FIRST EDITION 1992

### © TECH PUBLICATIONS PTE LTD, SINGAPORE

Copyright ©1992 Tech Publications Pte Ltd, #B1-39 Sim Lim Tower, Singapore 0820. World rights reserved. No part of this publication may be stored in a retrieval system, reproduced in any way, including but not limited to photocopy, photograph, magnetic or other record, without the prior agreement and written permission of the publisher.

Every effort has been made to supply complete and accurate information. However, TECH Publications Pte Ltd assumes no responsibility for its use, nor for any infringement of the intellectual property rights of third parties which would result from such use.

Printed in Singapore by TECH PUBLICATIONS PTE LTD, SINGAPORE for DE MUIDERKRING BV, WEESP, HOLLAND

Printed by Continental Press Pte Ltd, Singapore

## PREFACE

his microprocessor data hand book is the third revised edition of our earlier book. Since the first edition was published quite a bit of change has occurred in the industry. Many new chips and devices have also been added.

This new edition has been compiled after looking carefully in to various applications including personal computers, sophisticated instruments and communication systems.

It will also serve as a good reference book for computer hardware Hobbyists, Engineers and Educationists. It will help them identify all support chips applicable to specific microprocessor circuitry.

The publishers are thankful to various manufacturers of these devices whose datas have been used in this work.

The publishers are also grateful to Mr. A.K. Jain who have been very helpful in the compilation of this book.

Publishers

### CONTENTS

| DEVICE NO. | DEVICE FUNCTION                     | PAGE NO. |

|------------|-------------------------------------|----------|

| TTL DATA   |                                     |          |

| 7400       | Quad 2-NAND Gate                    | 1        |

| 7401       | Quad 2-NAND Gate                    | 2        |

| 7402       | Quad 2-NOR Gate                     | 3        |

| 7403       | Quad 2-NAND Gate                    | 4        |

| 7404       | Hex Inverter                        | 5        |

| 7405       | Hex Inverter                        | 6        |

| 7406, 7    | Hex Inverter, Hex Buffer            | 7        |

| 7408       | Quad 2-NAND Gate                    | 8        |

| 7409       | Quad 2-AND Gate                     | 9        |

| 7410, 11   | Triple 3-NAND Gate, AND Gate        | 10       |

| 7412       | Triple 3-NAND Gates                 | 11       |

| 7413       | Dual 4-NAND Schmitt Triggers        | 12       |

| 7414       | Hex Schmitt Trigger Inverters       | 13       |

| 7415       | Triple 3-AND Gate                   | 14       |

| 7416, 17   | Hex Inverter, Buffer                | 15       |

| 7420, 21   | Dual 4-NAND Gate                    | 16       |

| 7425       | Dual 4-NOR Gate                     | 17       |

| 7426       | Quad 2-NAND Buffer                  | 18       |

| 7427       | Triple 3-NOR Gate                   | 19       |

| 7428       | Quad 2-NOR Buffer                   | 20       |

| 7430       | 8-input NAND Gate                   | 21       |

| 7432       | Quad 2-OR Gate                      | 22       |

| 7433       | Quad 2-NOR Buffer                   | 23       |

| 7437       | Quad 2-NAND Buffer                  | 24       |

| 7438       | Quad 2-NAND Buffer                  | 25       |

| 7439       | Quad 2-NAND Buffer                  | 26       |

| 7440       | Dual 4-NAND Buffer                  | 27       |

| 7442       | BCD to Decimal Decoder              | 28       |

| 7445       | BCD-to-Decimal Decoder/Driver       | 29       |

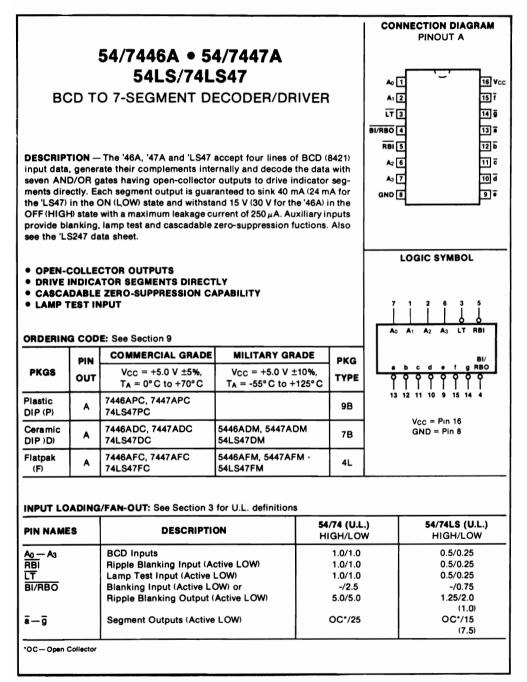

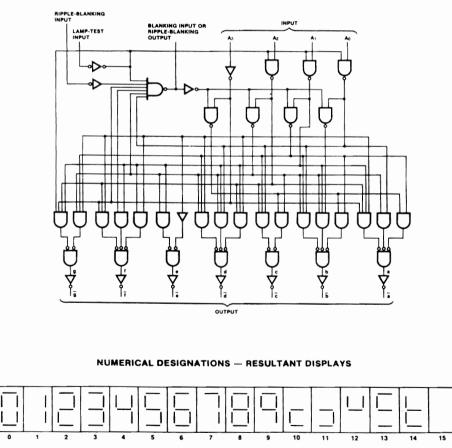

| 7446, 47   | BCD-to-seven Segment Decoder/Driver | 30       |

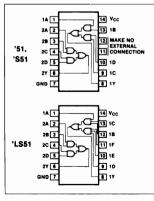

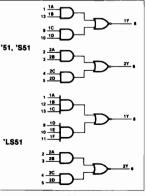

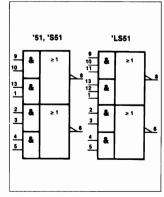

| 7451       | Dual 2-Wide 2-AOI Gate              | 33       |

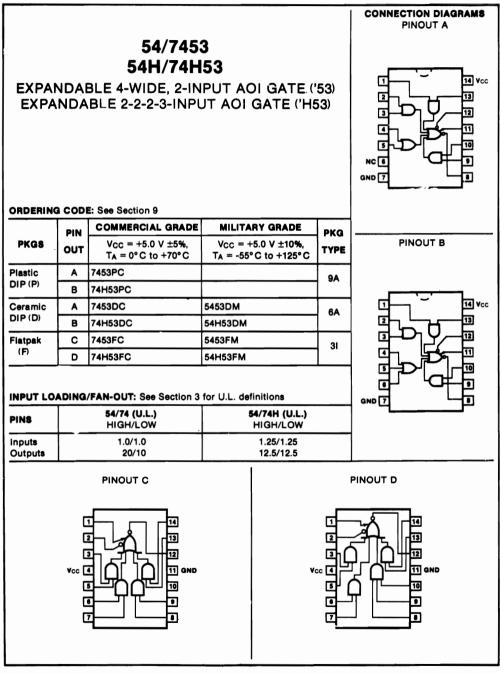

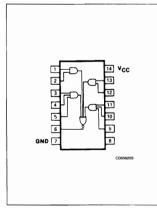

| 7453       | Expandable 4-wide 2-AOI Gate        | 34       |

| 7454       | 4-Wide 2-AOI Gate                   | 35       |

| 7464       | 4-Wide AOI Gate                     | 36       |

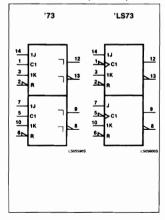

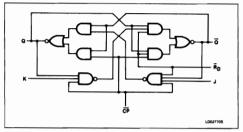

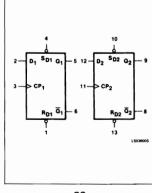

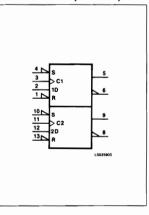

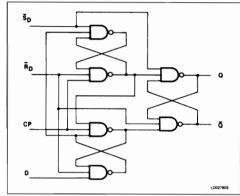

| 7473       | Dual JK Flip Flop                   | 37       |

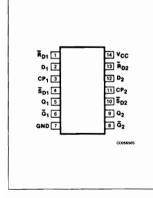

| 7474       | Dual D Flip Flop                    | 39       |

| 7475       | Quad Bistable latch                 | 41       |

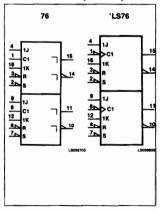

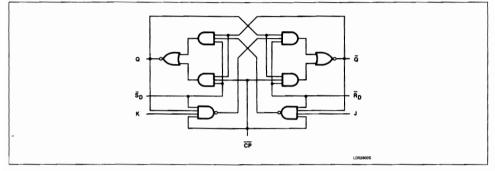

| 7476       | Dual JK Flip Flop                   | 42       |

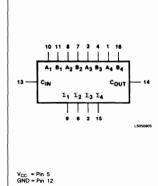

| 7483       | 4-Bit Full Adder                    | 44       |

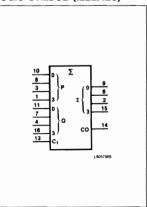

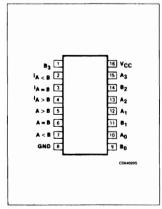

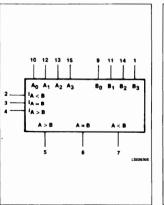

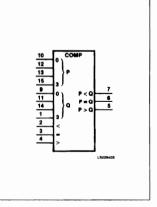

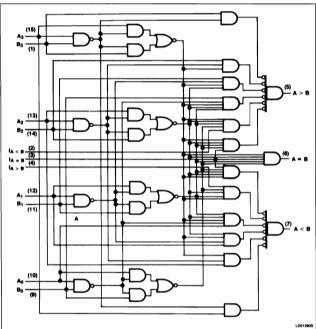

| 7485       | Comparators                         | 45       |

| 7486       | Quad 2-Exclusive or Gate            | 47       |

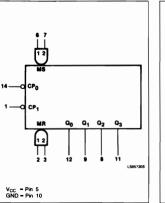

| 7490       | Decade Counter                      | 48       |

| 7491       | 8-Bit Shift Register                | 50       |

| 7492       | Divide by Twelve Counter            | 52       |

| 7493       | 4-Bit Binary Ripple Counter         | 54       |

| 7494       | 4-Bit Shift Register                | 56       |

|            | V                                   |          |

| TTL DATA                                                          |            |

|-------------------------------------------------------------------|------------|

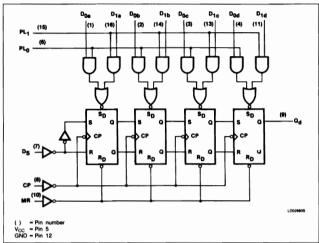

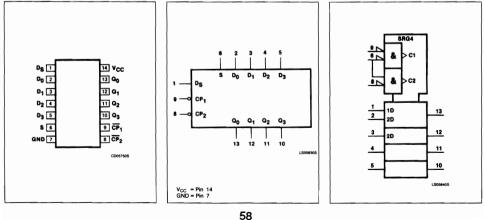

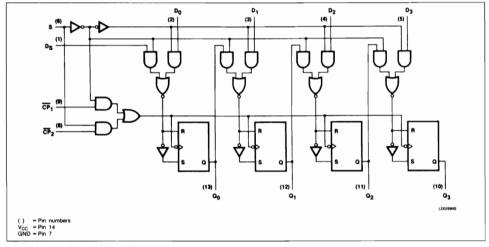

| 7495 4-Bit Shift Register                                         | 58         |

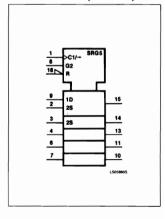

| 7496 5-Bit Shift Register                                         | 60         |

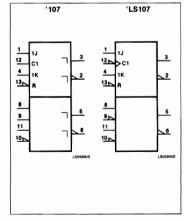

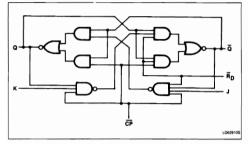

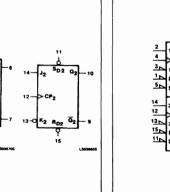

| 74107 Dual JK Flip, Flop                                          | 62         |

| 74109 Dual JK Flip Flop                                           | 64         |

| 74112 Dual JK Edge Triggered Flip Flop                            | 66         |

| 74113 Dual JK Edge Triggered Flip Flop                            | 68         |

| 74116 Dual 4-Bit Transparent latches                              | 70         |

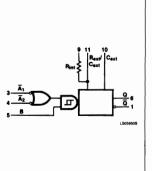

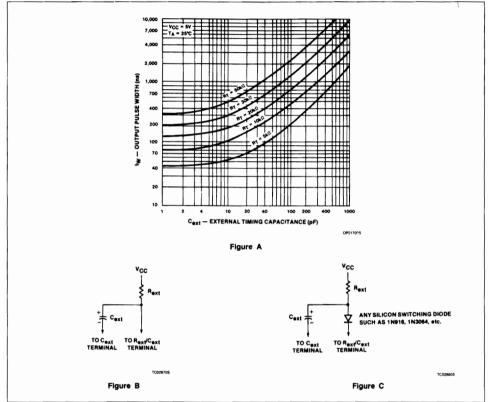

| 74121 Monostable Multivibrator                                    | 71         |

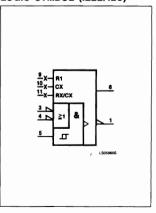

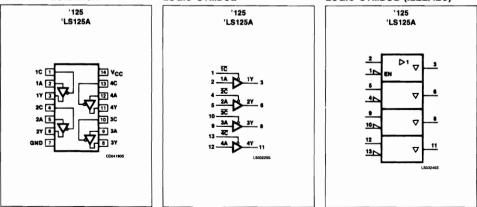

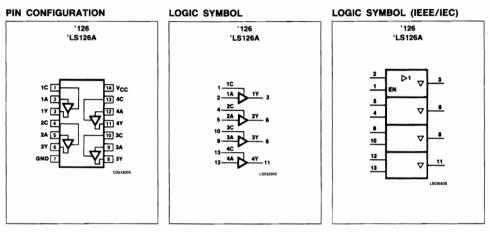

| 74123 Dual Monostable Multiviberator<br>74125 Quad 3 state Buffer | 73<br>76   |

| 74125 Quad 3 state Buller<br>74128 Quad 2-NOR Buffer              | 78<br>78   |

| 74132 Quad 2-NAND Schmitt Trigger                                 | 79         |

| 74133 13-NAND Gate                                                | 80         |

| 74134 12-NAND Gate                                                | 81         |

| 74135 Quad Exclusive OR/NOR Gate                                  | 82         |

| 74136 Quad 2-Exclusive or Gate                                    | 83         |

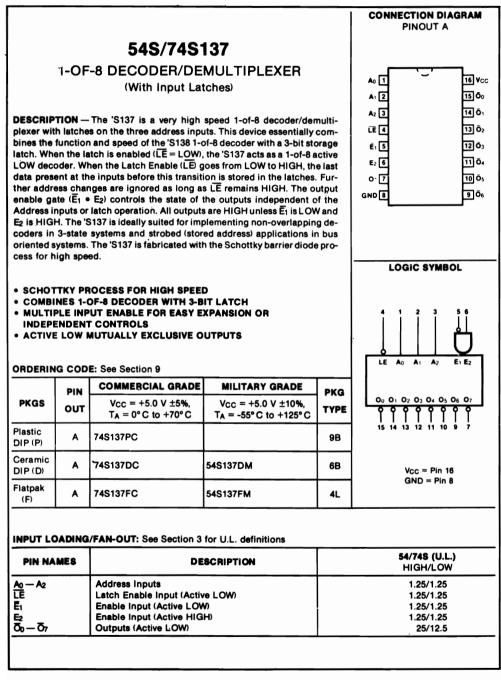

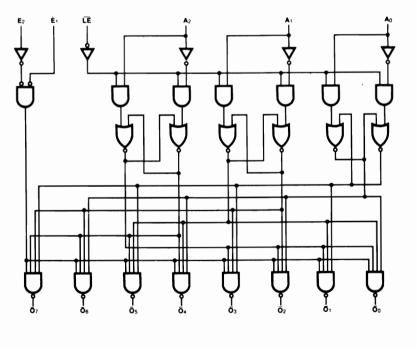

| 74137 1:8 Demultiplexer                                           | 84         |

| 74138 1:8 Demultiplexer                                           | 87         |

| 74139 Dual 1:4 Demultiplexer                                      | 89         |

| 74145 BCD-to-Decimal Decoder/Driver                               | 91         |

| 74147 Priority Encoder (Decimal to Binary)                        | 93         |

| 74148 Priority Encoder (Octal to Binary)                          | 95<br>07   |

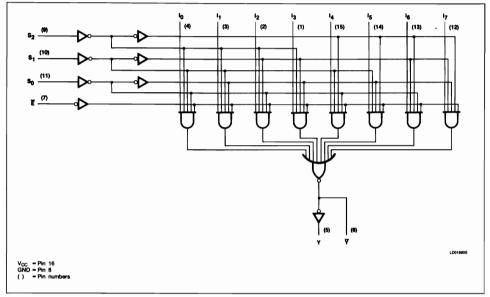

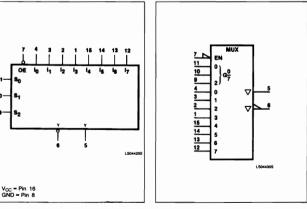

| 74150 16:1 Multiplexer<br>74151 8:1 Multiplexer                   | 97<br>99   |

| 74151 0.1 Multiplexer<br>74153 Dual 4:1 Multiplexer               | 99<br>101  |

| 74154 1 : 16 Demultiplexer                                        | 103        |

| 74155 Dual 1:4 Demultiplexer                                      | 105        |

| 74156 Dual 1:4 Demultiplexer                                      | 107        |

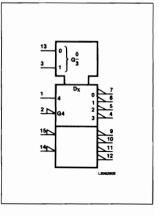

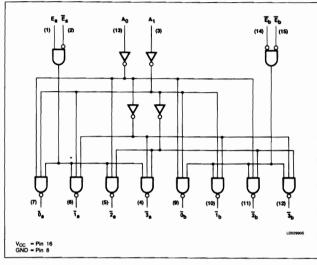

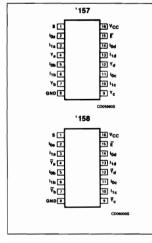

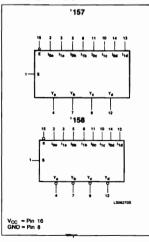

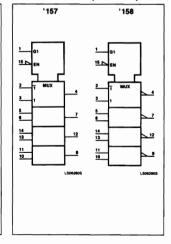

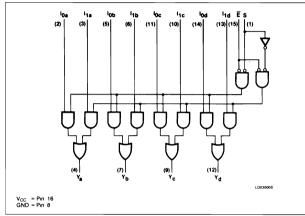

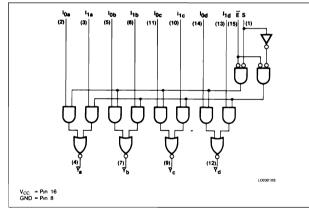

| 74157, 158 Quad 2:1 Multiplexer                                   | 109        |

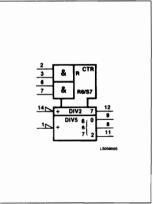

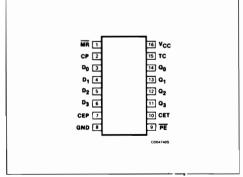

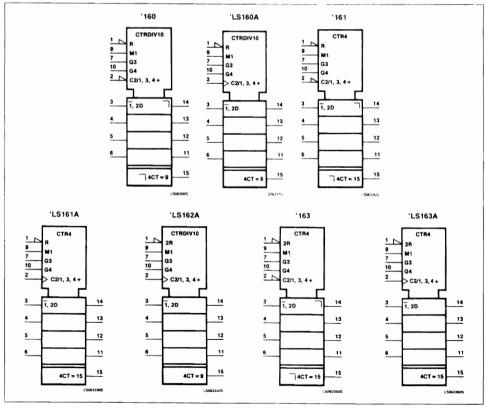

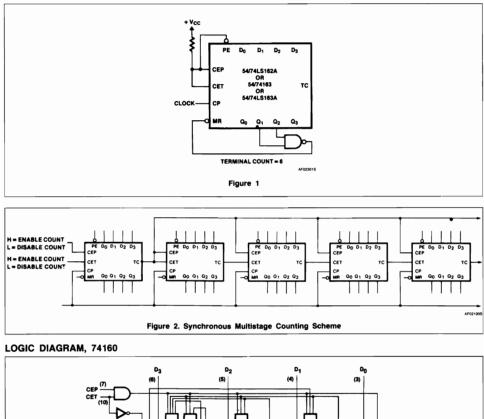

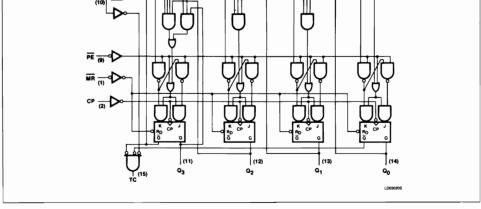

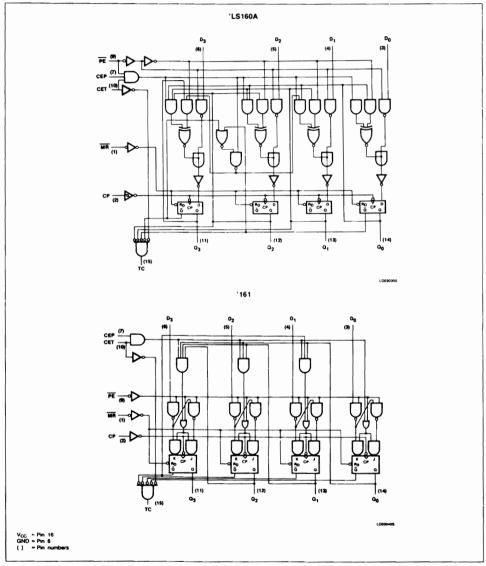

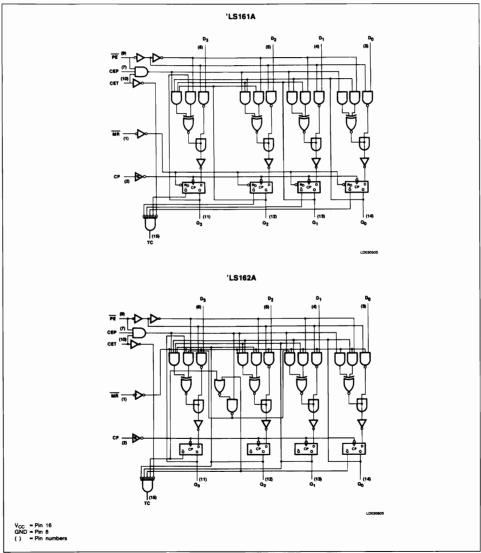

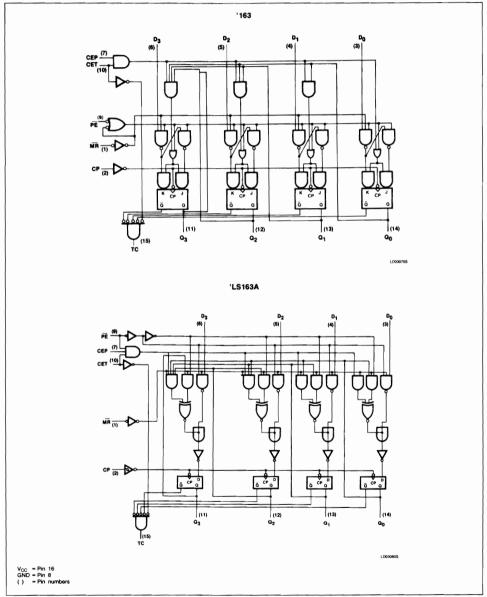

| 74160, 61, 62, 63 Counters                                        | 111        |

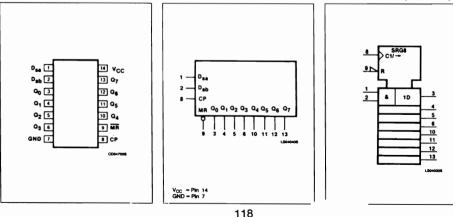

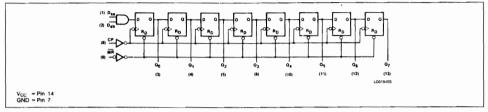

| 74164 8 Bit Shift Register                                        | 118        |

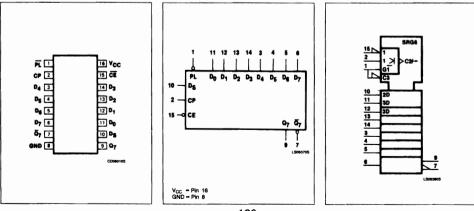

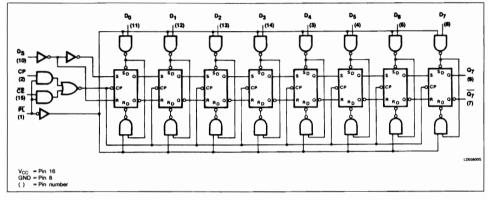

| 74165 8 Bit Shift Register                                        | 120        |

| 74166 8 Bit Shift Register                                        | 122        |

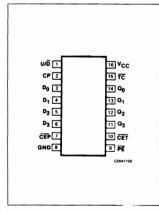

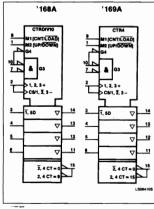

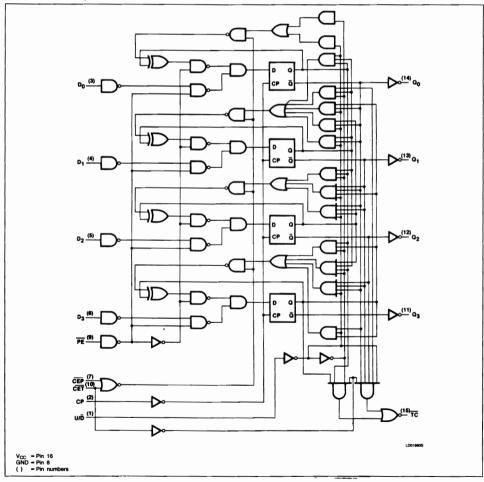

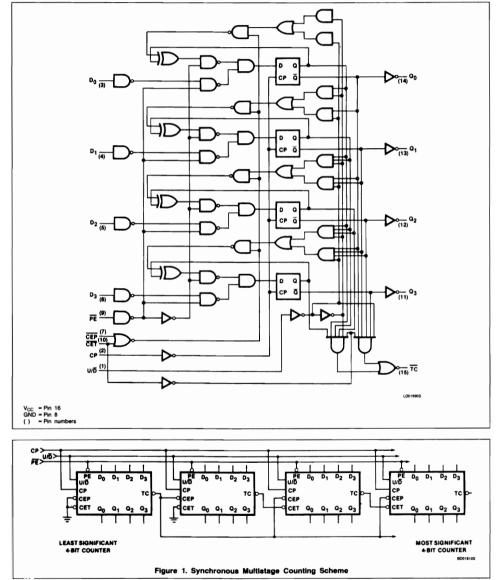

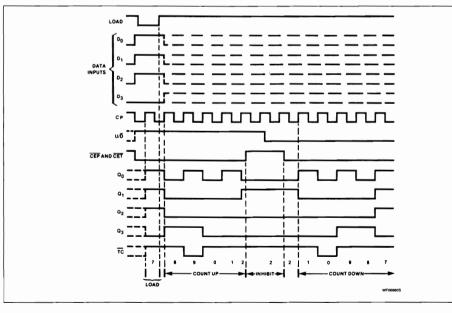

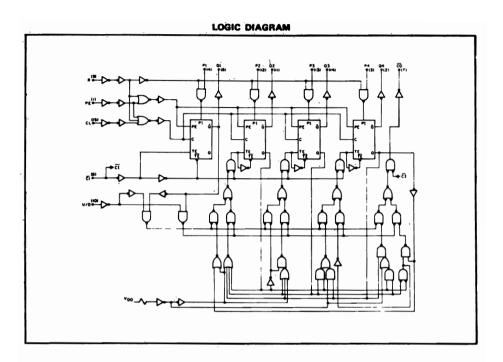

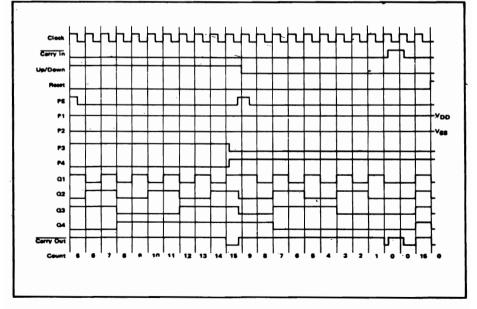

| 74168, 69 4 Bit Up/Down Synchronous Counter                       | 124        |

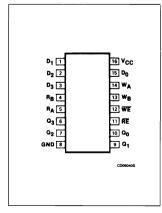

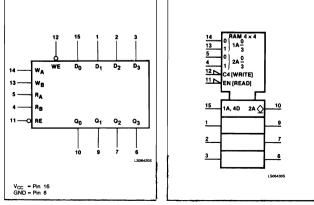

| 74170 4x4 Register Files                                          | 128<br>129 |

| 74173 Quad D-type Flip Flop                                       | 129        |

| 74174 Hex D Flip Flop<br>74175 Quad D Flip Flop                   | 133        |

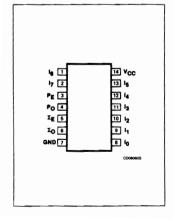

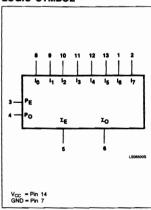

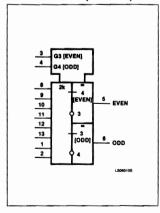

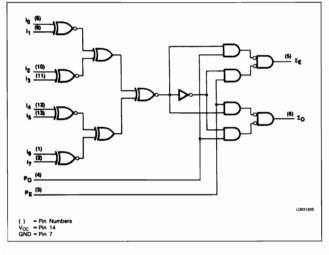

| 74180 8 Bit Parity Generator                                      | 135        |

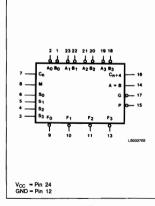

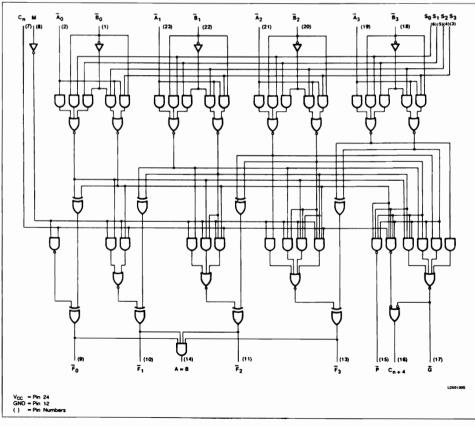

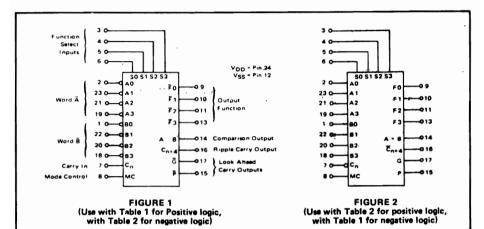

| 74181 Arithmetic Logic Unit                                       | 137        |

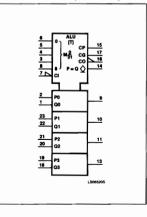

| 74182 Carry Generator                                             | 140        |

| 74190, 91 Counters                                                | 142        |

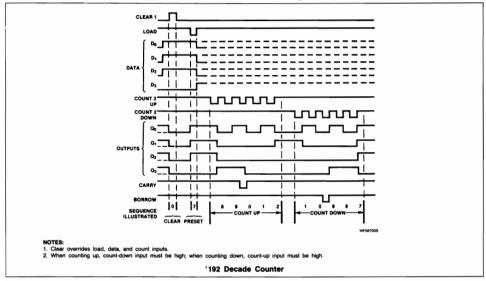

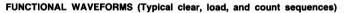

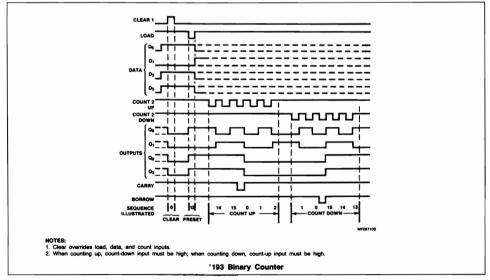

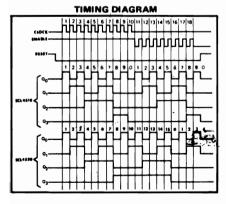

| 74192, 93 Counters                                                | 147        |

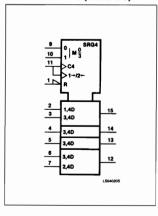

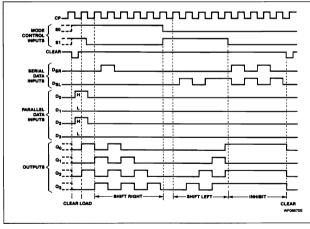

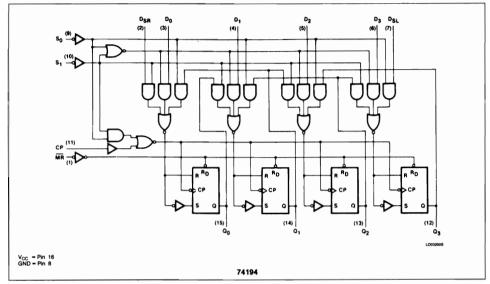

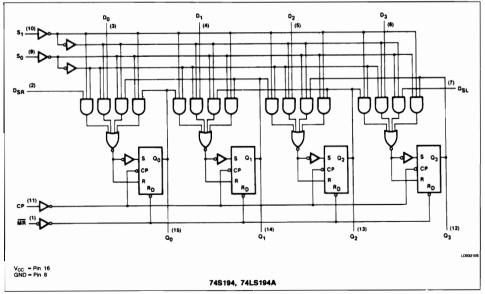

| 74194 Shift Register                                              | 151        |

| 74195 Shift Register                                              | 154        |

PAGE NO.

DEVICE NO.

**DEVICE FUNCTION**

vi

| DEVICE NO.        | DEVICE FUNCTION                      | PAGE NO. |

|-------------------|--------------------------------------|----------|

| TTL DATA          |                                      |          |

| 74197             | Pre settable 4-Bit Binary Counter    | 156      |

| 74199             | 8-Bit Parallel-Access Shift Register | 158      |

| 74245             | Ocal Tansceiver                      | 161      |

| 74251             | 8-Input Multiplexer                  | 162      |

| 74253             | Dual 4-Input Multiplexer             | 164      |

| 74256             | Dual 4-Bit Addressable latch         | 165      |

| 74258             | Data Selector/Multiplexer            | 166      |

| 74259             | 8-Bit Addressable latch              | 168      |

| 74266             | Quad 2-Exclusive NOR Gate            | 170      |

| 74273             | Octal D Flip Flop                    | 171      |

| 74283             | 4-Bit Full Adder                     | 172      |

| 74290             | Decade Counter                       | 174      |

| 74293             | 4-Bit Binary Ripple Counter          | 176      |

| 74364             | Octal D Flip Flop                    | 178      |

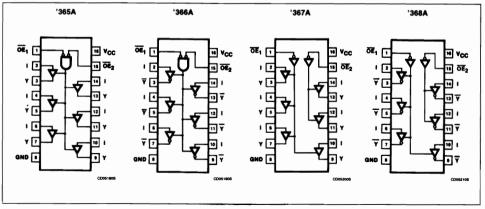

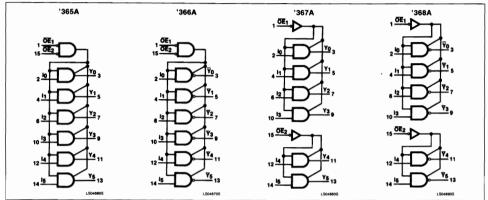

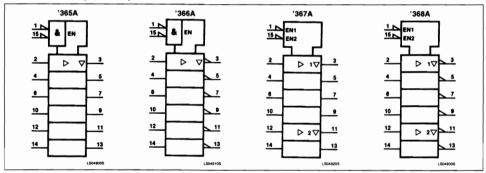

| 74365, 66, 67, 68 | Buffer Drivers                       | 179      |

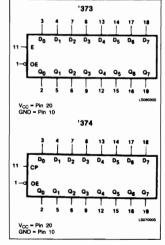

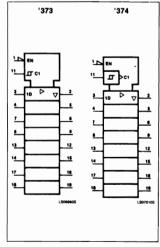

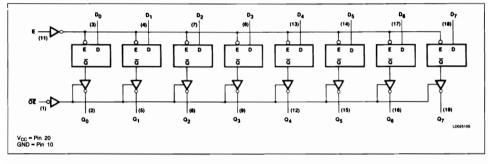

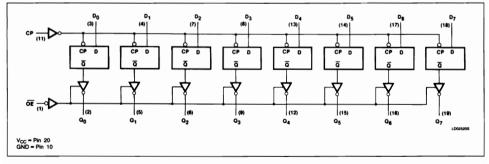

| 74373, 74         | Latches/Flip Flop                    | 181      |

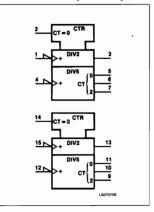

| 74390             | Dual Decade Ripple Counter           | 183      |

| 74393             | Dual 4-Bit Binary Ripple Counter     | 185      |

| CMOS              |                                      |          |

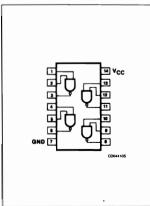

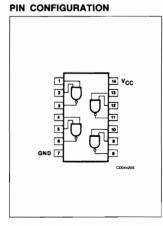

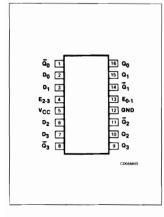

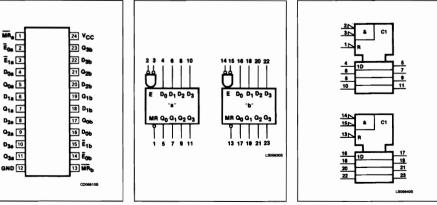

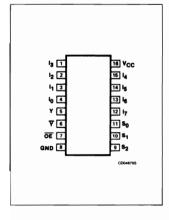

| CD4000            | Series Pinconfiguration              | 187      |

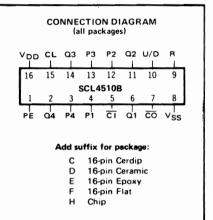

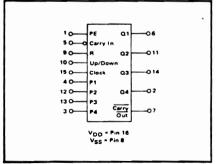

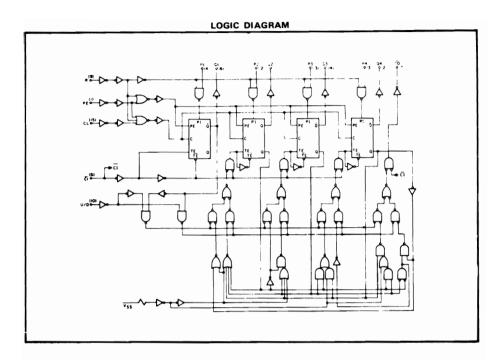

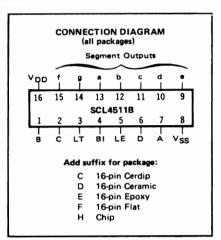

| 4510              | BCD Up/Down Counter                  | 201      |

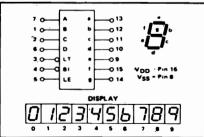

| 4511              | BCD to Seven Segment Decoder         | 203      |

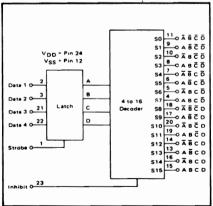

| 4514              | 4-16 Line Decoder                    | 205      |

| 4516              | Binary Up/Down Counter               | 206      |

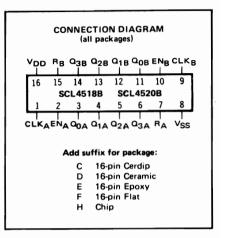

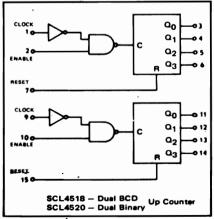

| 4518              | Dual Up Counter                      | 208      |

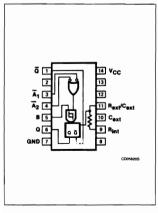

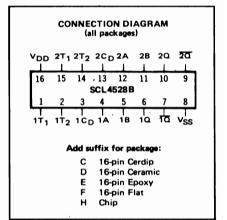

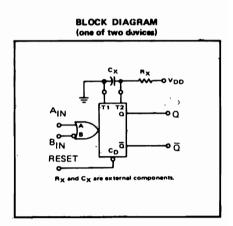

| 4528              | Mono Stable Multivibrator            | 209      |

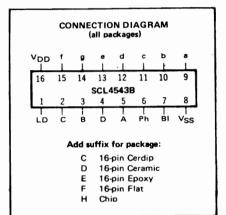

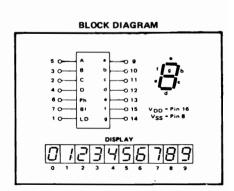

| 4543              | BCD to 7 Segment Decoder             | 210      |

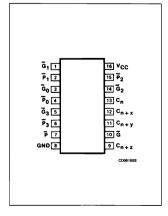

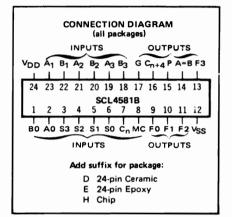

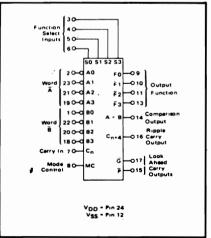

| 4581              | 4-Bit Arithmetic logic unit          | 211      |

| 8 BIT CPUs        |                                      |          |

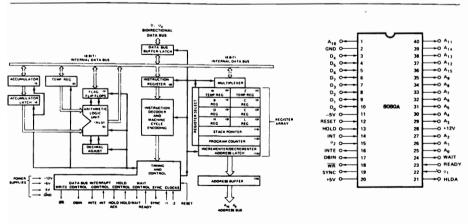

| 8080              | 8 Bit Microprocessor                 | 213      |

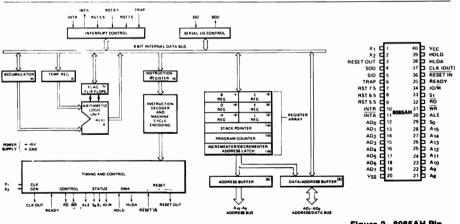

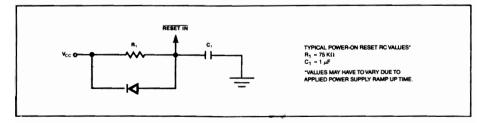

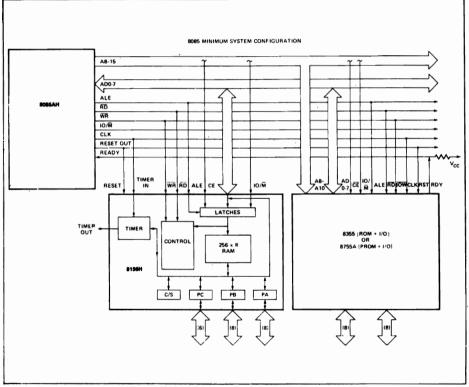

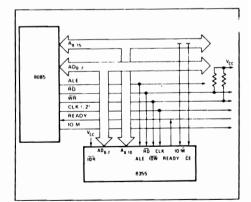

| 8085              | 8 Bit Microprocessor                 | 218      |

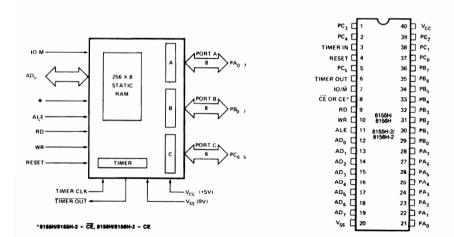

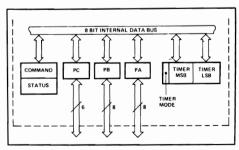

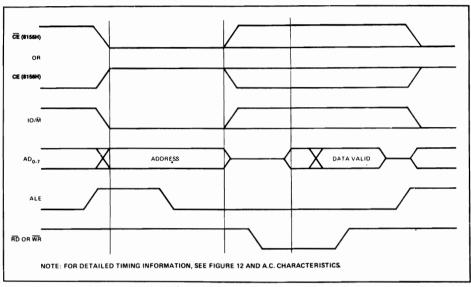

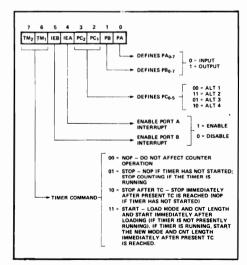

| 8155              | 2 K RAM with I/O Ports and Timer     | 231      |

| 8185              | I K Ram                              | 239      |

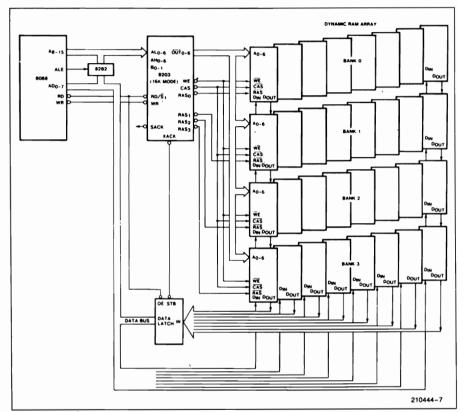

| 8202              | Dynamic RAM Controller               | 241      |

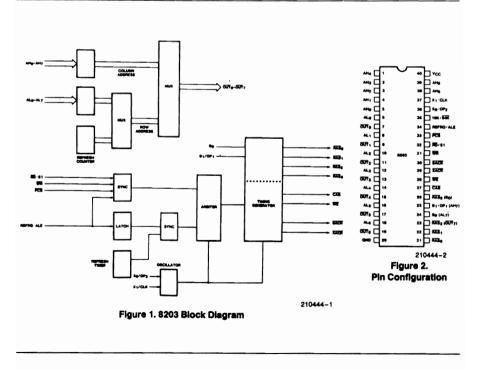

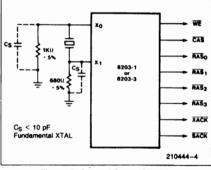

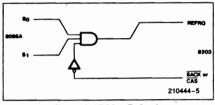

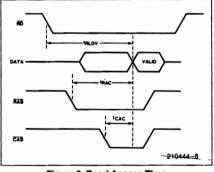

| 8203              | Dynamic RAM Controller               | 242      |

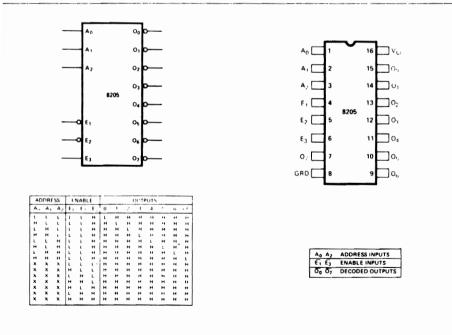

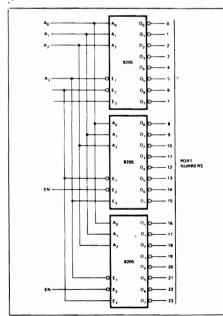

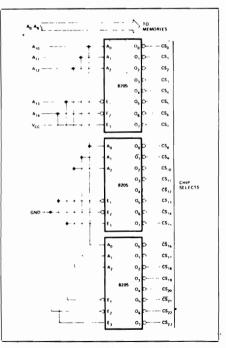

| 8205              | 1:8 Decoder                          | 249      |

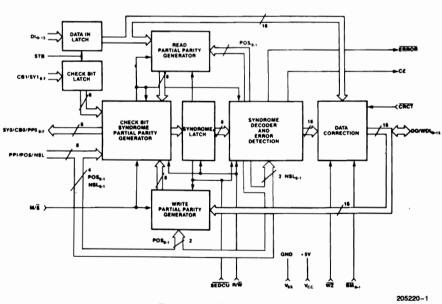

| 8206              | Error Detection & Correction Unit    | 251      |

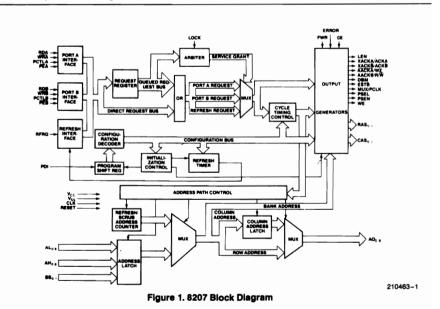

| 8207              | Dual Port Dynamic RAM Controller     | 253      |

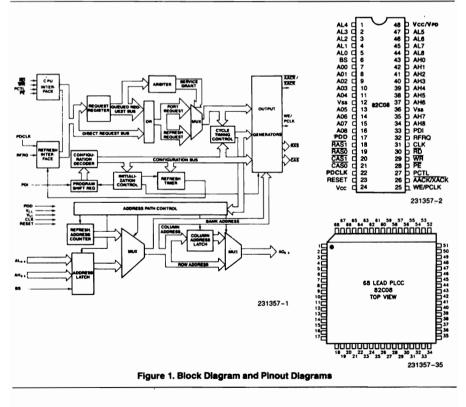

| 8208              | Dynamic RAM Controller               | 254      |

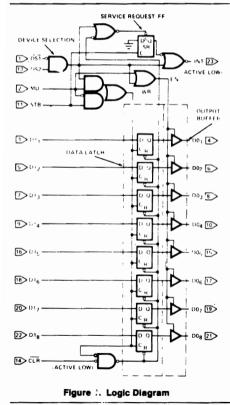

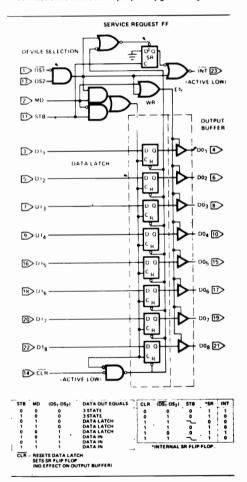

| 8212              | 8 Bit I/O Port                       | 255      |

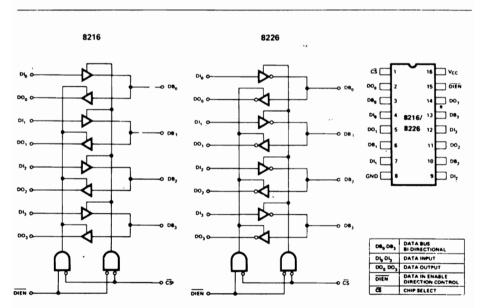

| 8216              | 4 Bit Bus Driver                     | 257      |

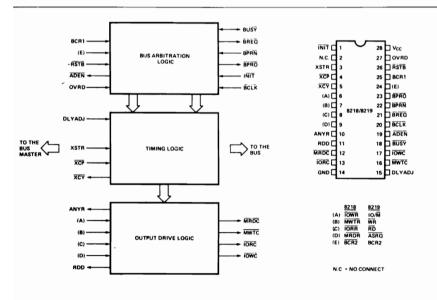

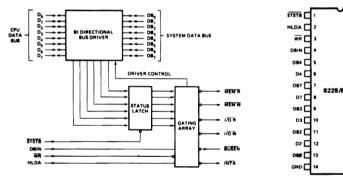

| 8218              | Bus Controller                       | 258      |

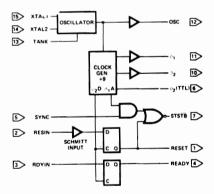

| 8224              | Clock generator                      | 259      |

### DEVICE NO. DEVICE FUNCTION

| 8 BIT CPUs   |                                            |            |

|--------------|--------------------------------------------|------------|

| 8228         | System Controller                          | 260        |

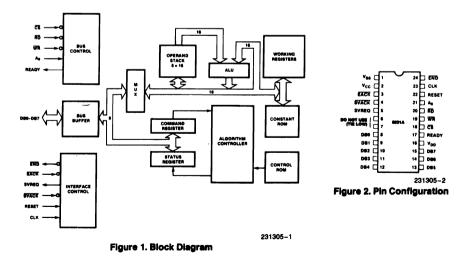

| 8231         | Arithmetic Processing Unit                 | 261        |

| 8232         | Floating Point Processing Unit             | 262        |

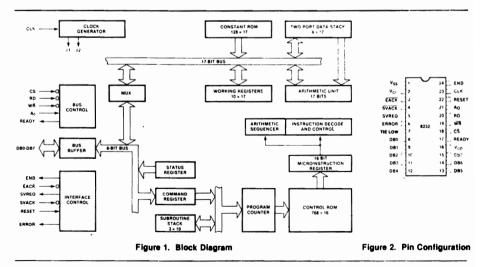

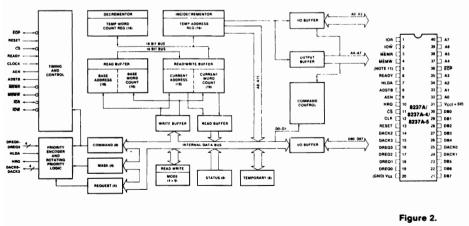

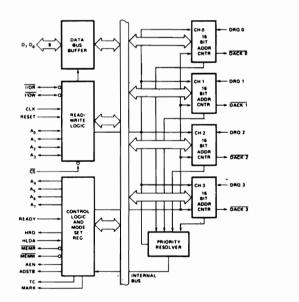

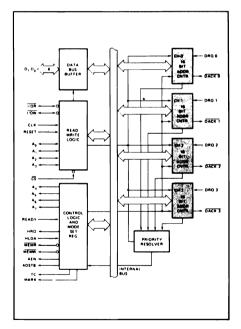

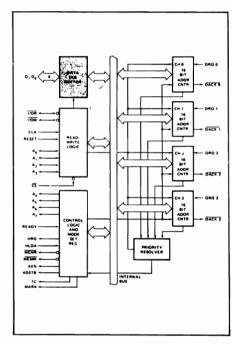

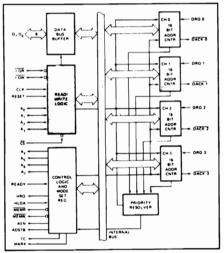

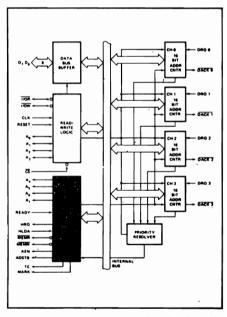

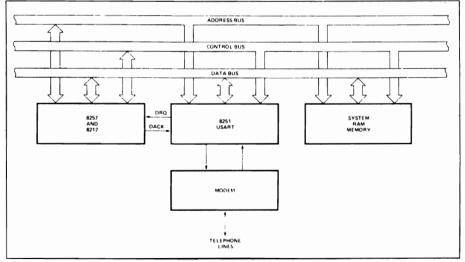

| 8237         | Programmable DMA Controller                | 263        |

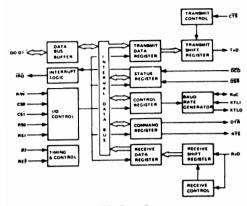

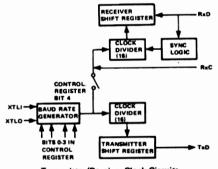

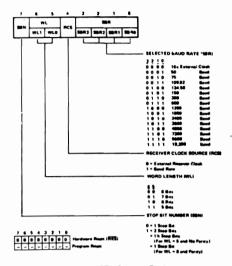

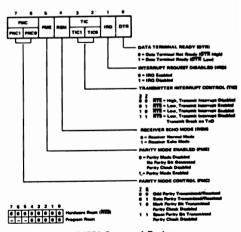

| 8250         | Asynchronous Communication Element         | 270        |

| 8251         | Programmable Communication Interface       | 273        |

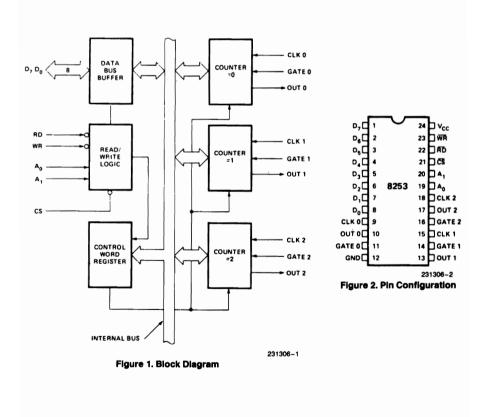

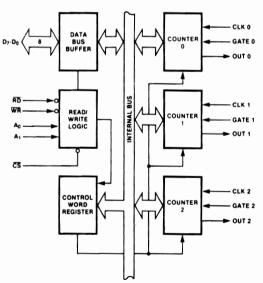

| 8253         | Programmable Interval Timer                | 284        |

| 8254         | Programmable Interval Timer                | 285        |

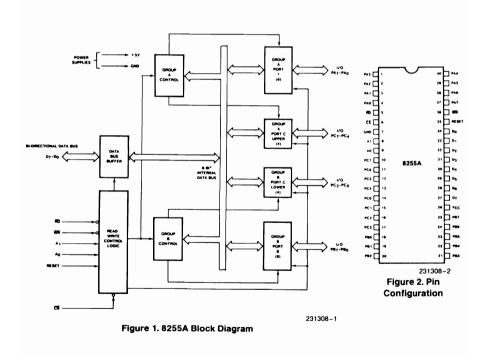

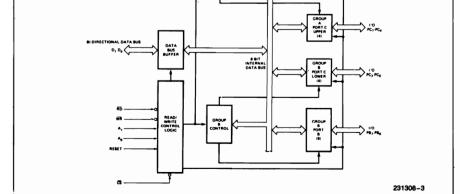

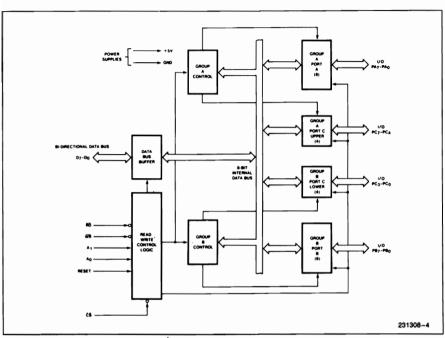

| 8255         | Programmable Peripheral Interface          | 286        |

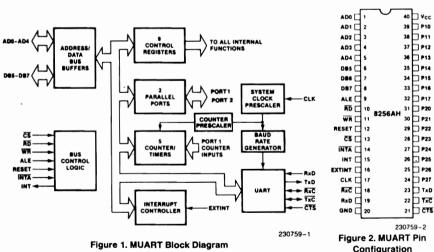

| 8256         | Support Controller                         | 304        |

| 8257         | Programmable DMA Controller                | 305        |

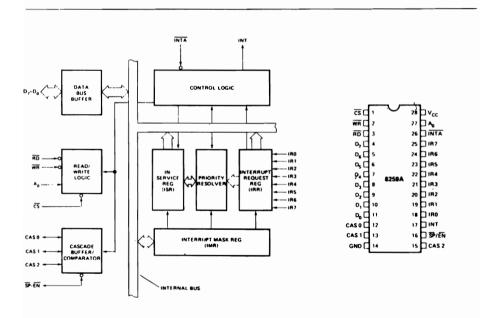

| 8259         | Programmable Interrupt Controller          | 315        |

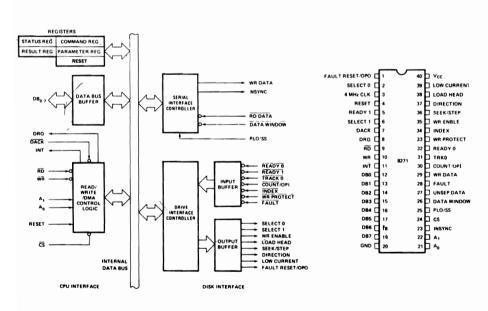

| 8271         | Floppy Disk Controller                     | 316        |

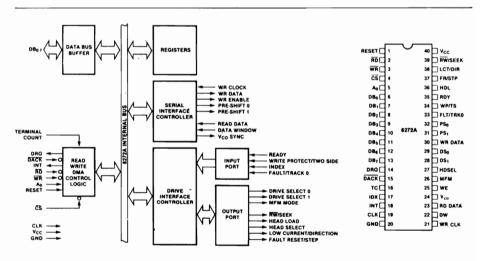

| 8272         | Floppy Disk Controller                     | 317        |

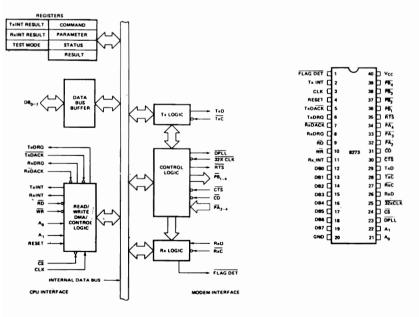

| 8273         | Protocol Controller                        | 318        |

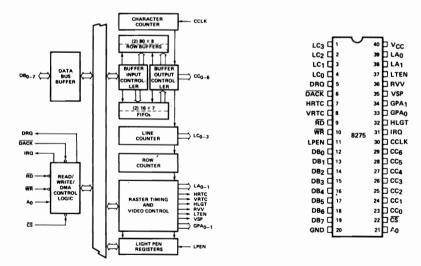

| 8275         | CRT Controller                             | 319        |

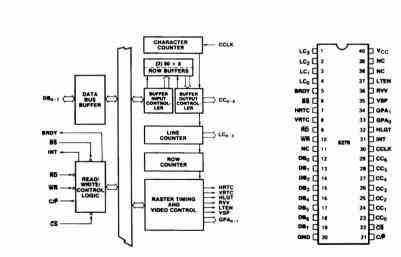

| 8276         | CRT Controller                             | 320        |

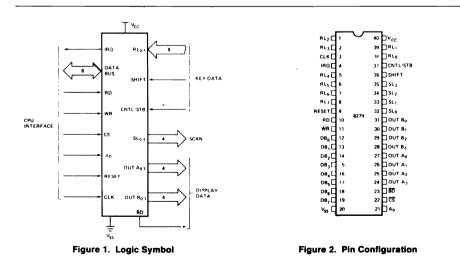

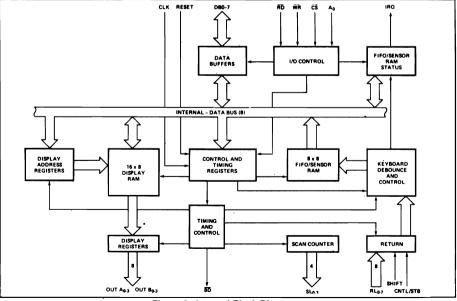

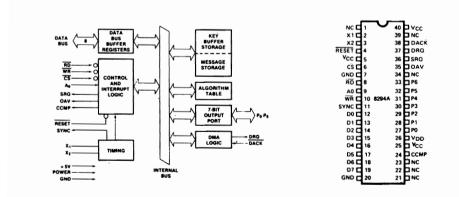

| 8279         | Keyboard/Display Interface                 | 321        |

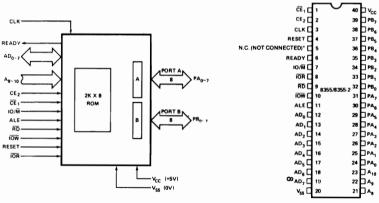

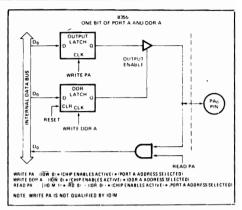

| 8355         | 2K RAM with I/O                            | 329        |

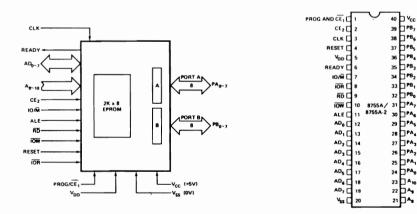

| 8755         | 2K EPROM with I/O                          | 331        |

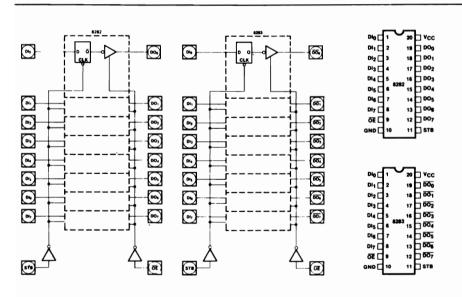

| 8282         | Octal latch                                | 332        |

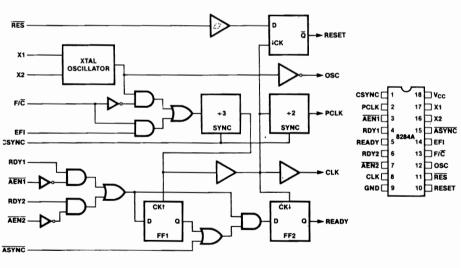

| 8284         | Clock generator                            | 333        |

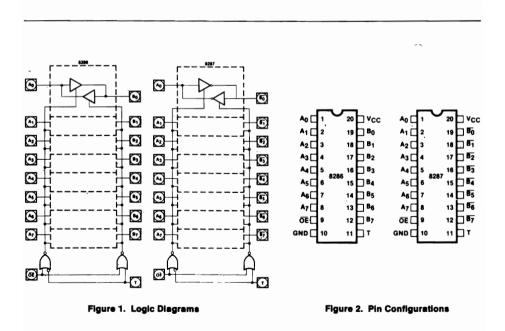

| 8286, 87     | Octal Bus Transceiver                      | 334        |

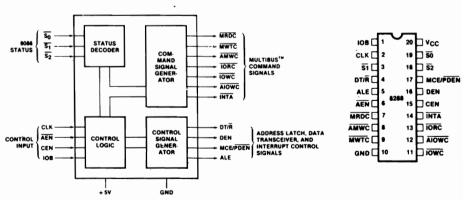

| 8288         | Bus Controller                             | 335        |

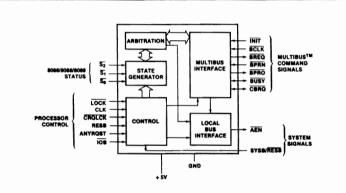

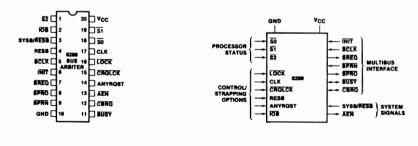

| 8289         | Bus Aribter                                | 336        |

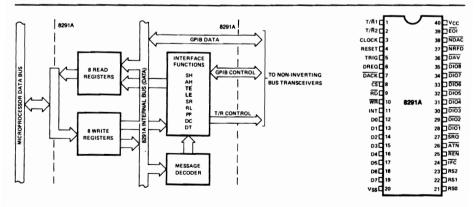

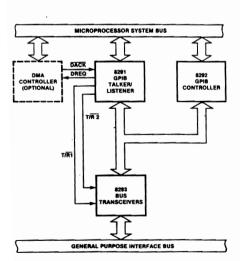

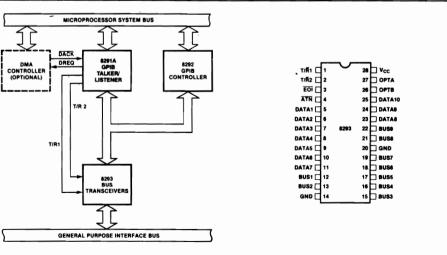

| 8291         | GPIB Talker/Listener                       | 337        |

| 8292         | GPIB Controller                            | 338<br>339 |

| 8293         | GPIB Transceiver                           | 339        |

| 8294         | DATA Encryption unit                       | 340        |

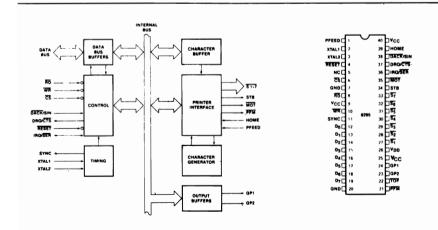

| 8295<br>8041 | Dot Matrix Printer Controller              | 342        |

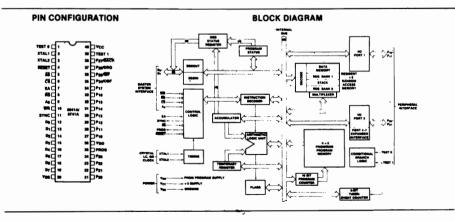

|              | 8 Bit Microcomputer                        | 343        |

| 8048<br>8051 | 8 Bit Microcomputer<br>8 Bit Microcomputer | 347        |

| 8052         | BASIC Interpreter                          | 351        |

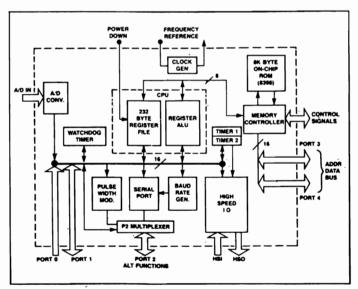

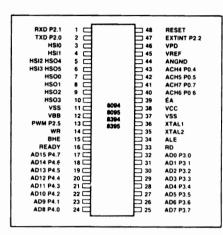

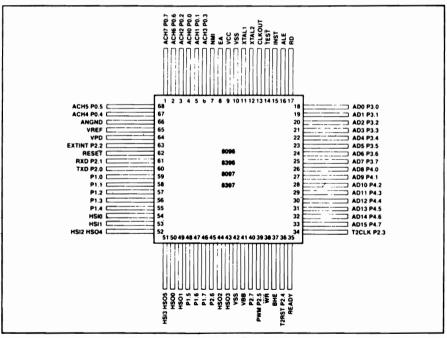

| 8094         | 16 Bit Micro Controller                    | 355        |

| 6800         | 8 Bit Microprocessing Unit                 | 357        |

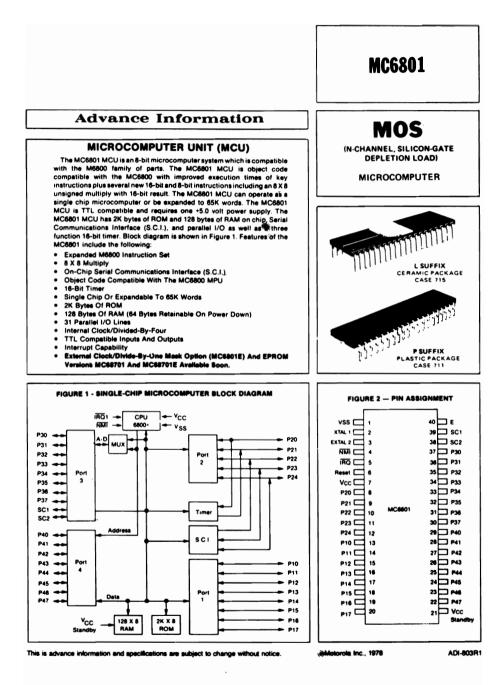

| 6801         | Microcomputer Unit                         | 365        |

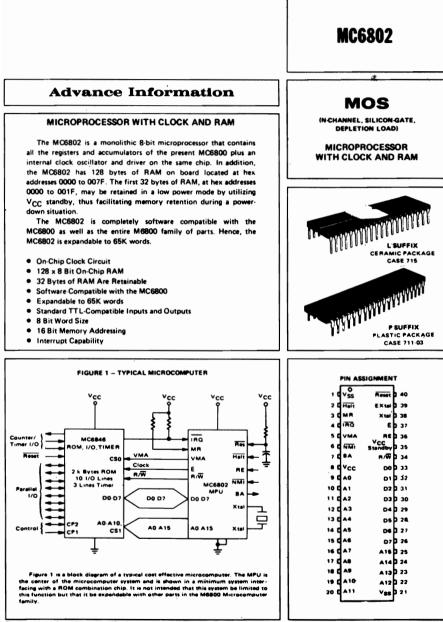

| 6802         | Microprocessor with CLK & RAM              | 366        |

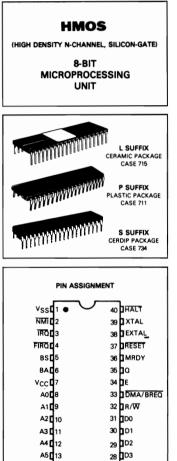

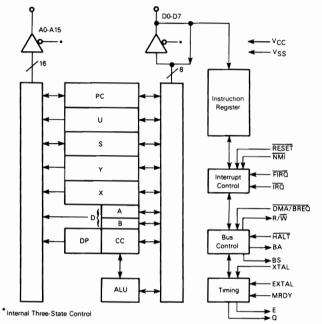

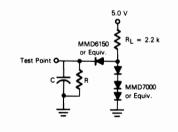

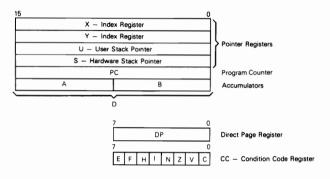

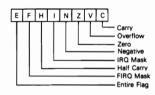

| 6809         | High Performance Microprocessor            | 367        |

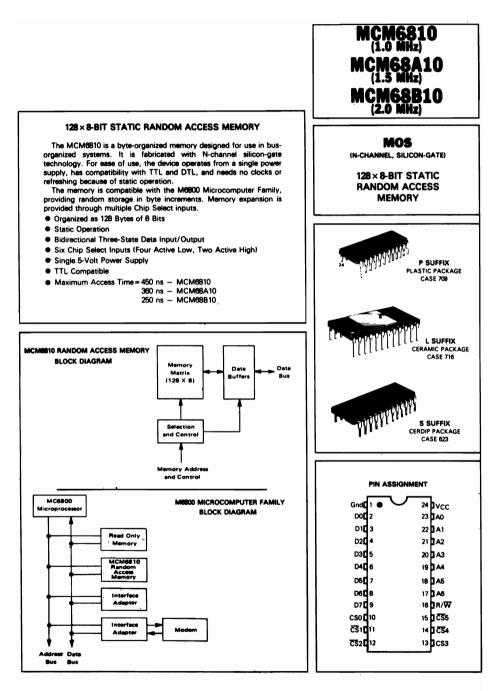

| 6810         | 128x8 Bit RAM                              | 371        |

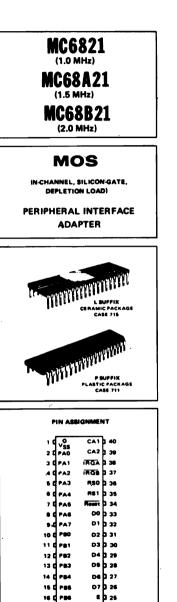

| 6821         | Peripheral Interface Adaptor               | 372        |

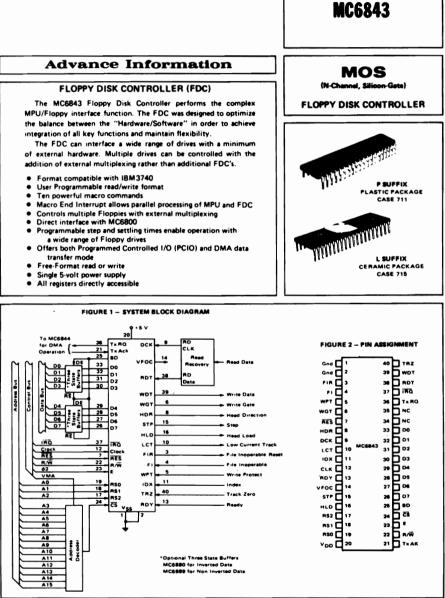

| 6843         | Floppy Disk Controller                     | 373        |

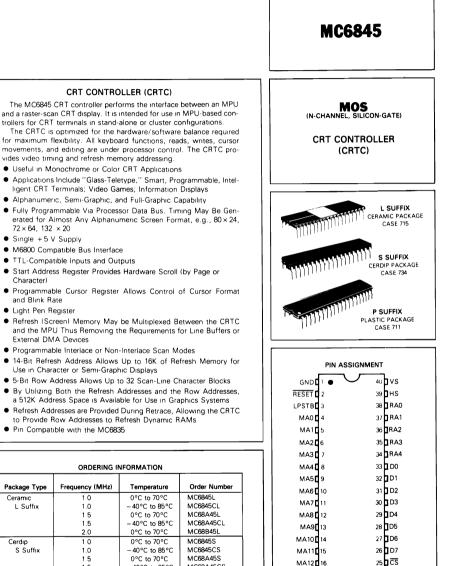

| 6845         | CRT Controller                             | 374        |

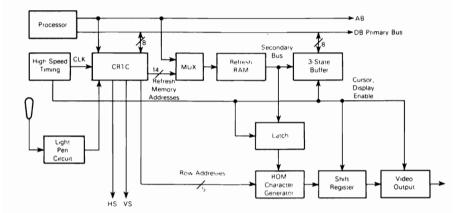

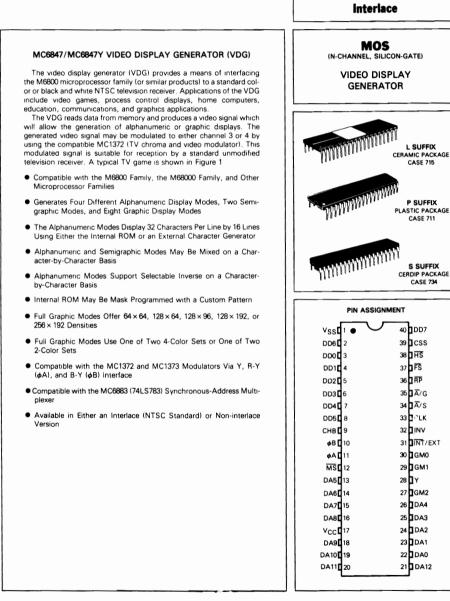

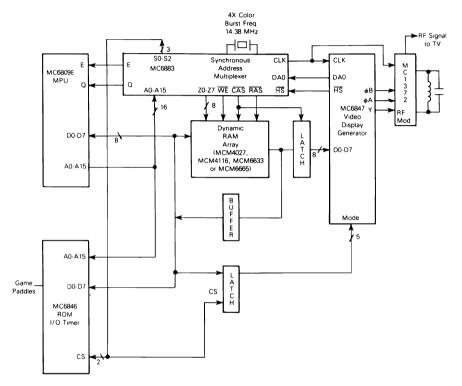

| 6847         | Video Display Generator                    | 376        |

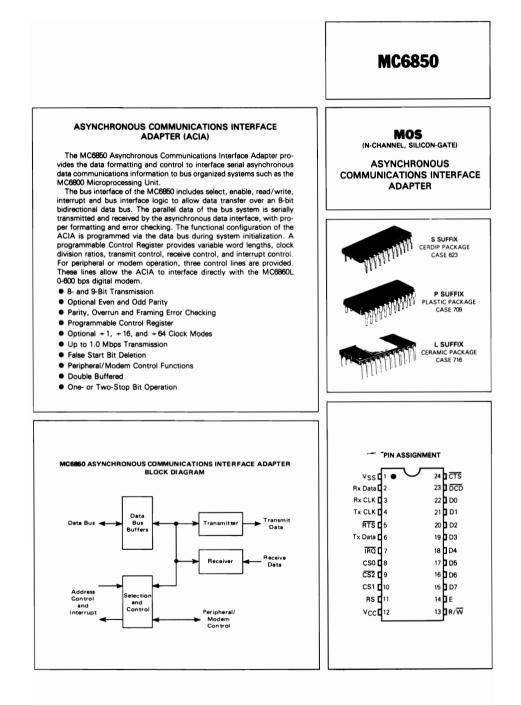

| 6850         | ACIA                                       | 378        |

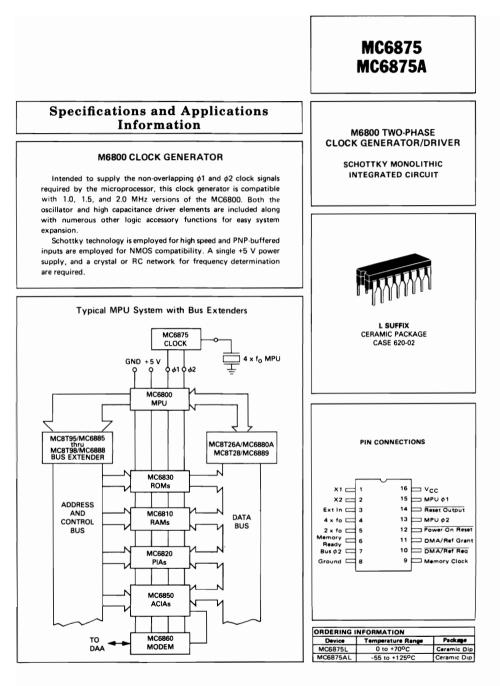

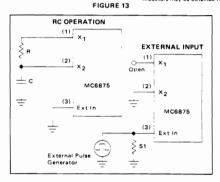

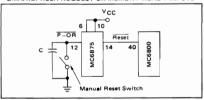

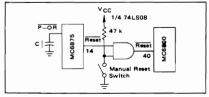

| 6875         | Clock Generator                            | 379        |

|              |                                            |            |

| DEVICE NO.       | DEVICE FUNCTION                      | PAGE NO. |

|------------------|--------------------------------------|----------|

| 8 BIT CPUs       |                                      |          |

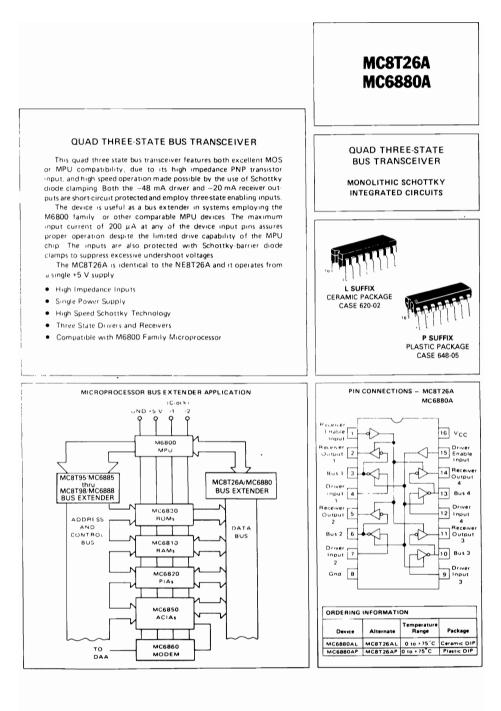

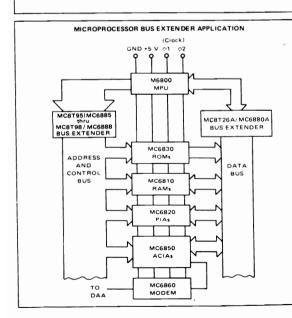

| 6880             | Bus Transceiver                      | 381      |

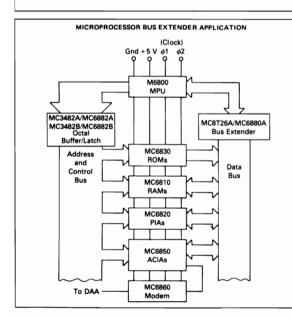

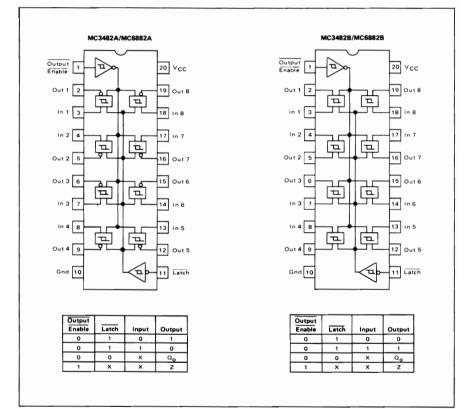

| 6882             | Tri state Buffer/latch               | 382      |

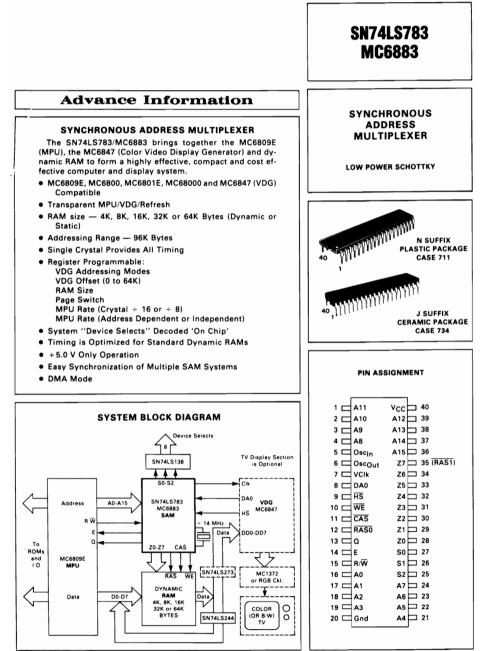

| 6883             | Address Multiplexer                  | 384      |

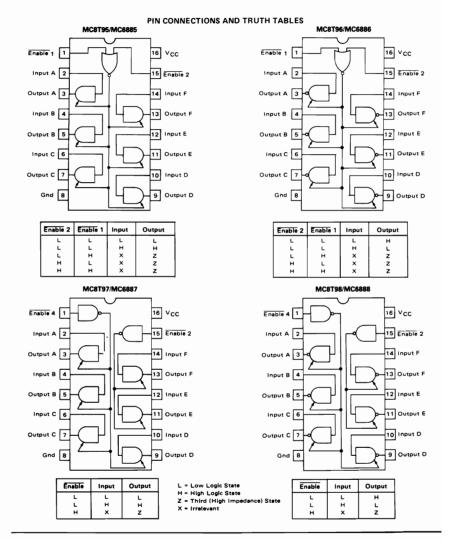

| 6885             | Address Bus Extender                 | 385      |

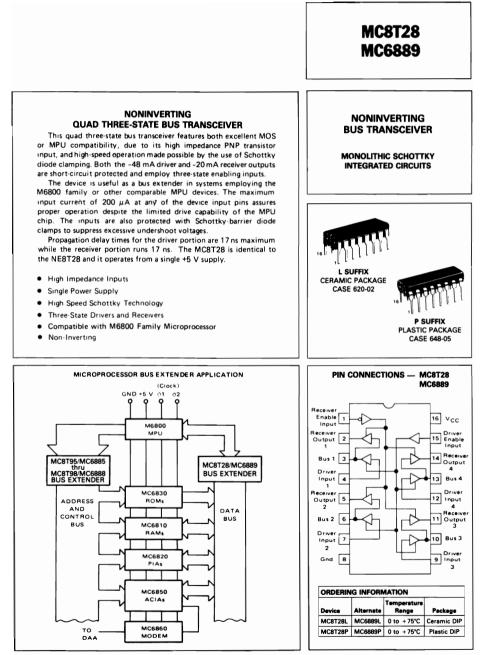

| 6889             | Bus Transceiver                      | 387      |

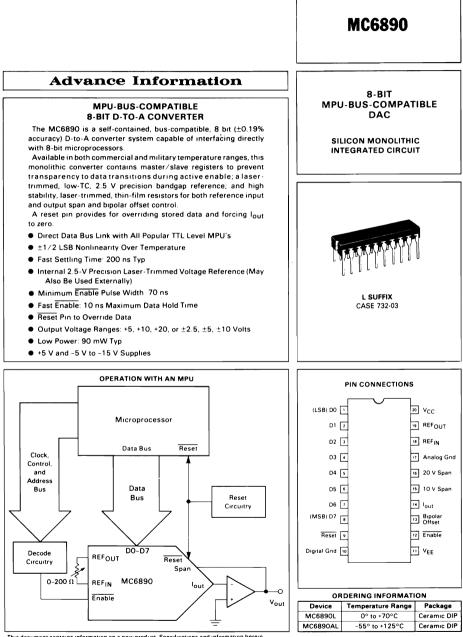

| 6890             | 8 Bit D/A Convertor                  | 388      |

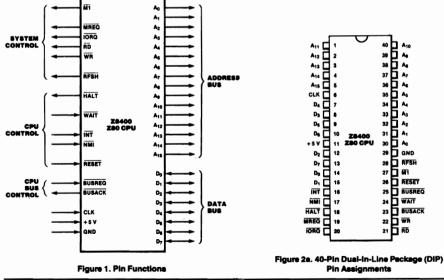

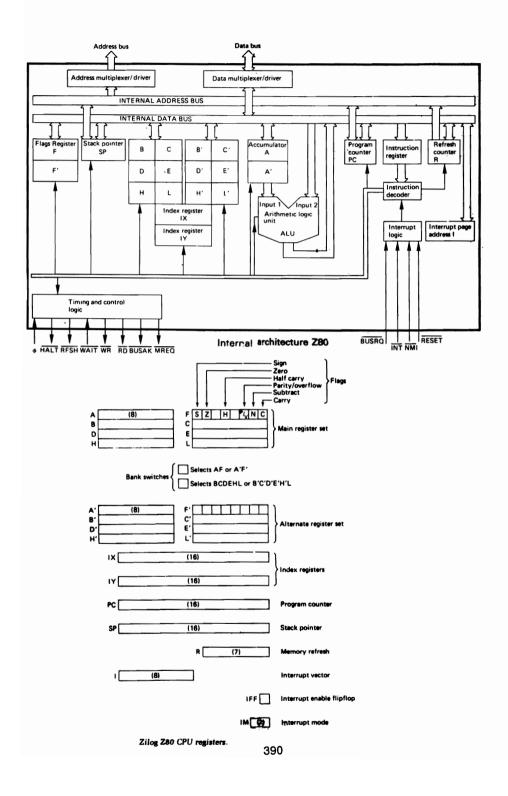

| 8400             | Z 80 CPU                             | 389      |

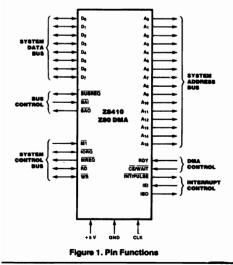

| 8410             | Z 80 DMA                             | 393      |

| 8420             | Z 80 PIO                             | 394      |

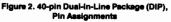

| 8430             | Z 80 CTC                             | 395      |

| 8440             | Z 80 SIO                             | 396      |

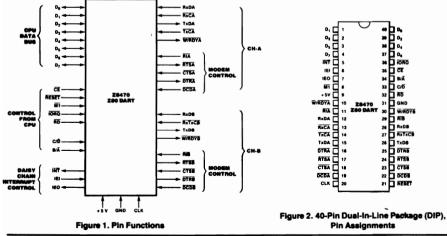

| 8470             | Z 80 DART                            | 397      |

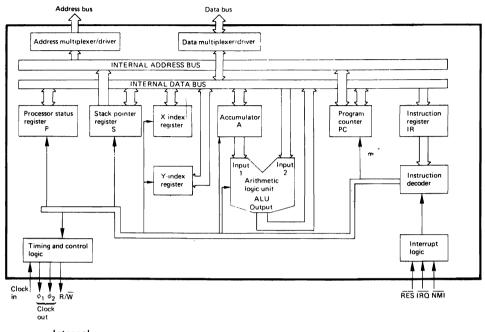

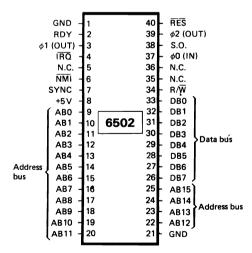

| 6502             | Rocwell 8 Bit CPU                    | 398      |

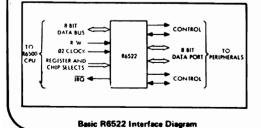

| 6522             | VIA                                  | 401      |

| 6545             | CRT Controller                       | 403      |

| 6551             | ACIA                                 | 405      |

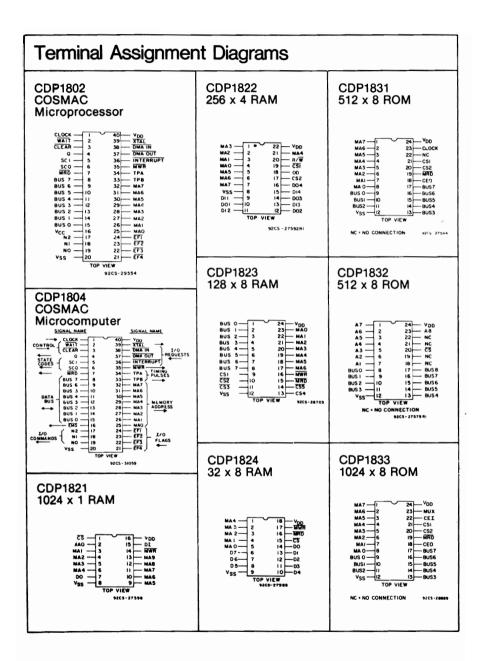

| CDPI1802         | RCA 8 Bit Microprocessor             | 407      |

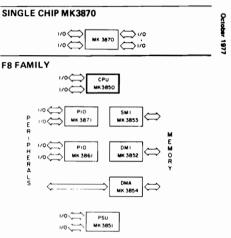

| F8               | Mostek Central Processing Unit       | 414      |

| 16/32 Bit Microp | processor                            |          |

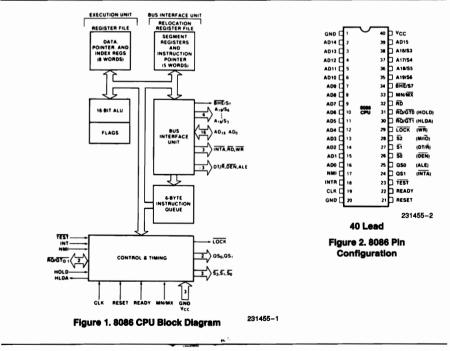

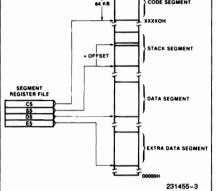

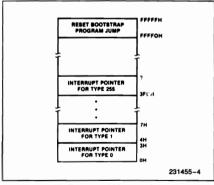

| 8086             | 16 Bit Microprocessor                | 415      |

| 8088             | 8/16 Bit Microprocessor              | 433      |

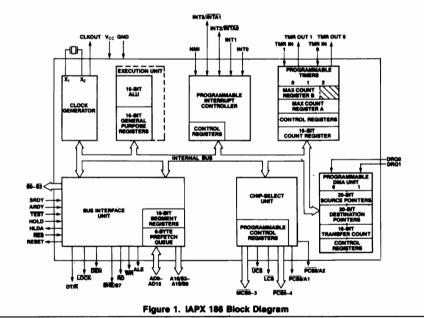

| 80186            | 16 Bit Microprocessor                | 448      |

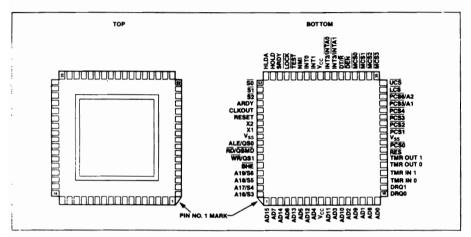

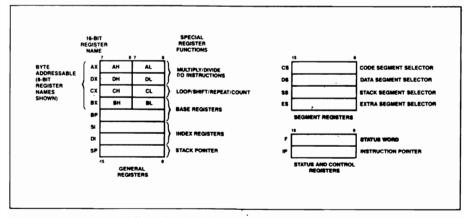

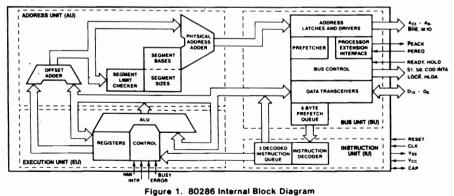

| 80286            | 16 Bit Microprocessor                | 454      |

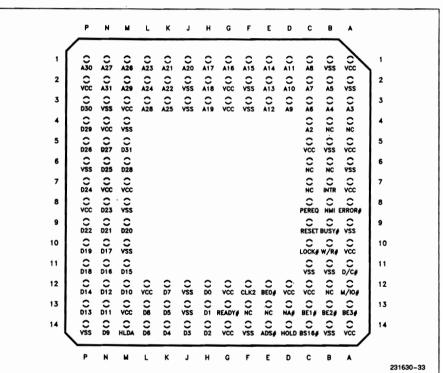

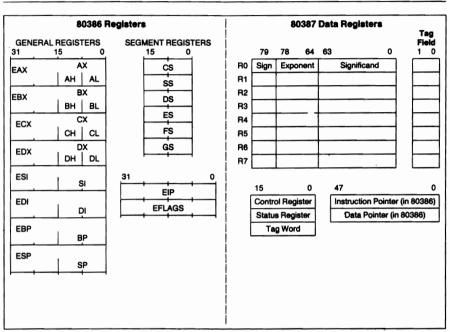

| 80386            | 32 Bit Microprocessor                | 458      |

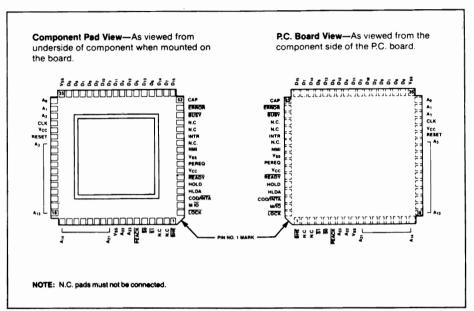

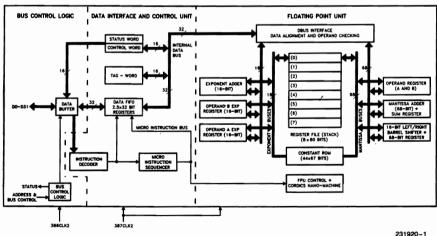

| 80387            | 80 Bit Numeric Processor             | 486      |

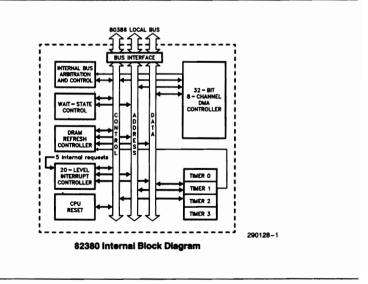

| 82380            | 32 Bit DMA Controller                | 488      |

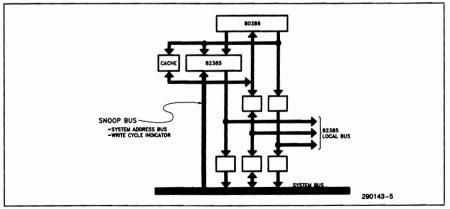

| 82385            | 32 Bit Cache Controller              | 491      |

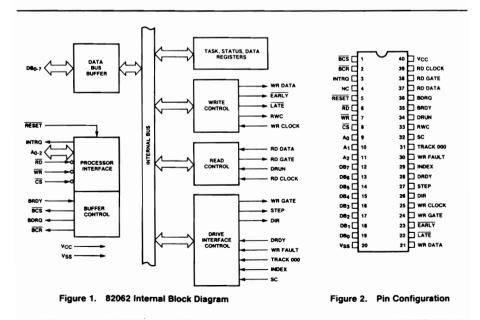

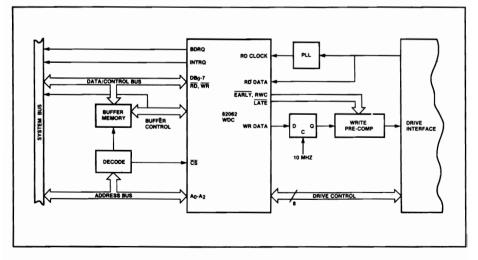

| 82062            | Winchester Disk Controller           | 496      |

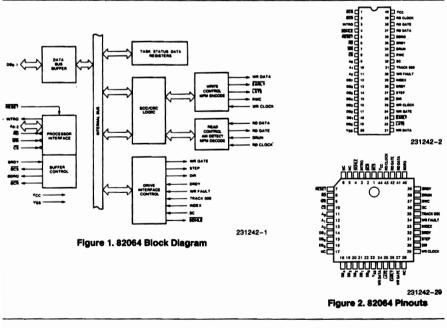

| 82064            | Winchester Disk Controller           | 498      |

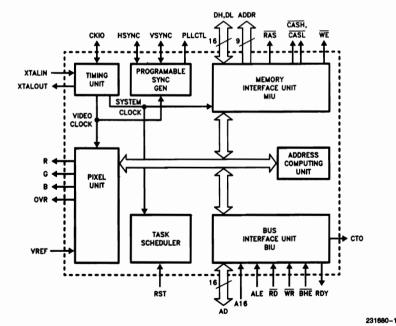

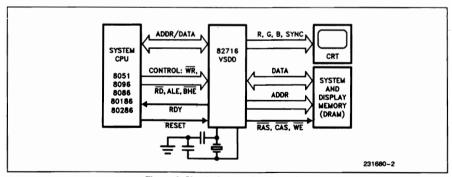

| 82716            | Video Storage & Display Device       | 500      |

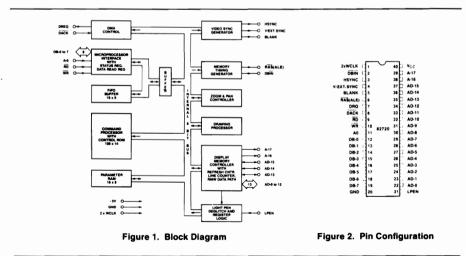

| 82720            | Graphic Display Controller           | 502      |

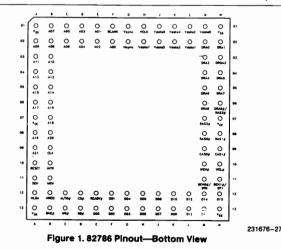

| 82786            | Graphic Coprocessor                  | 503      |

| 80486            | 32 Bit Microprocessor                | 504      |

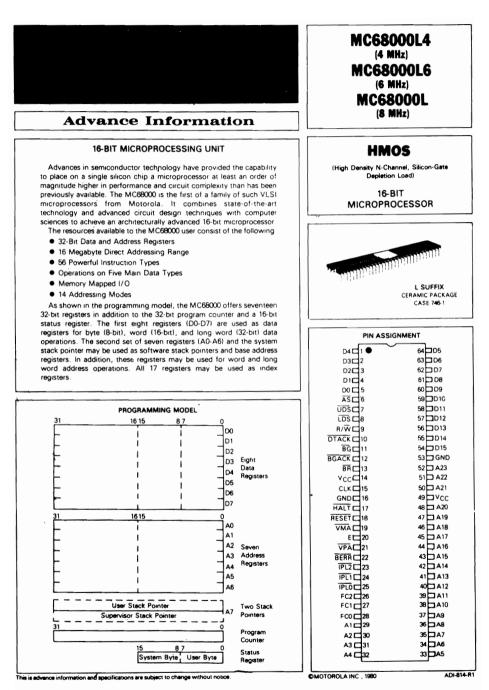

| 68000            | 16 Bit Microprocessor                | 514      |

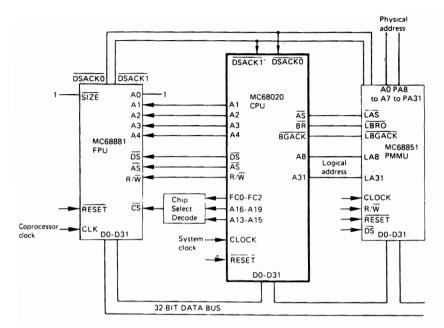

| 68020            | 32 Bit Virtual Memory Microprocessor | 554      |

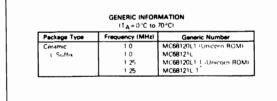

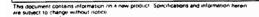

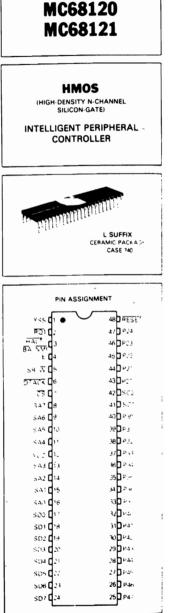

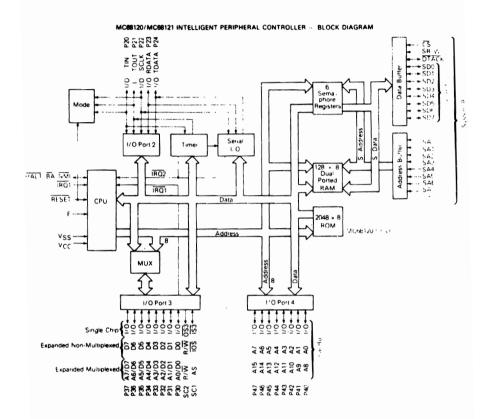

| 68120            | Peripheral Controller                | 555      |

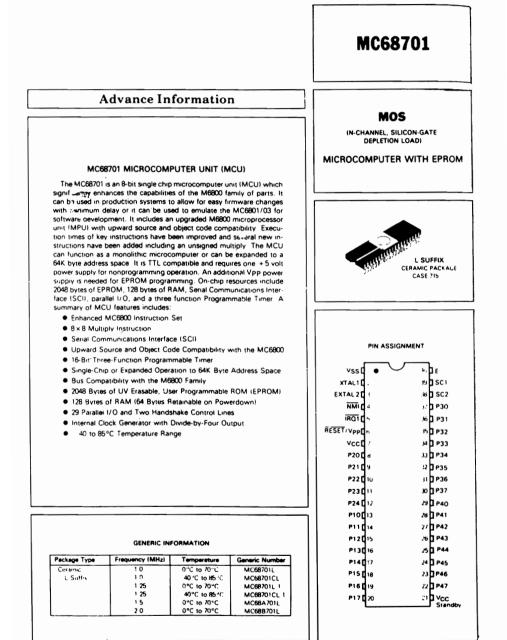

| 68701            | Microcomputer Unit                   | 557      |

| 68881            | Floating Point Co-processor          | 559      |

| 68851            | Memory Management Unit               | 563      |

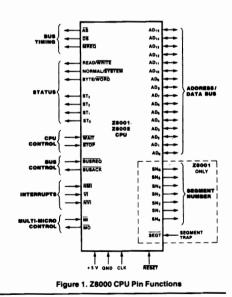

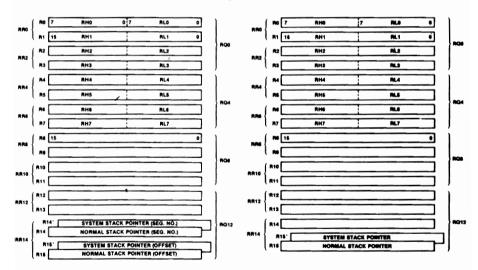

| Z 8000           | 16 Bit CPU                           | 566      |

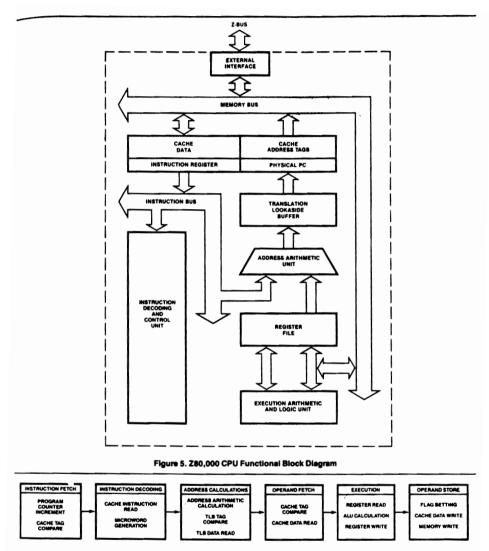

| Z 80000          | 32 Bit CPU                           | 576      |

|                  | ix                                   |          |

| DEVICE NO.     | DEVICE FUNCTION           | PAGE NO. |

|----------------|---------------------------|----------|

| MEMORY CHIPs   |                           |          |

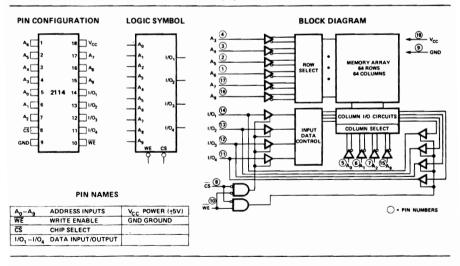

| 2114           | IK x 4 Bit RAM            | 583      |

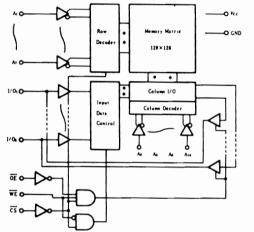

| 6116           | 2K x 8 Bit RAM            | 584      |

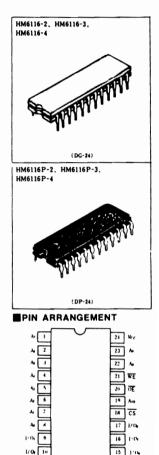

| 65116          | 2K x 8 Bit RAM            | 585      |

| 6264           | 8K x 8 Bit RAM            | 586      |

| 63256          | 32K x 8 Bit RAM           | 587      |

| 84256          | 32K x 8 Bit RAM           | 588      |

| 55257          | 32K x 8 Bit RAM           | 589      |

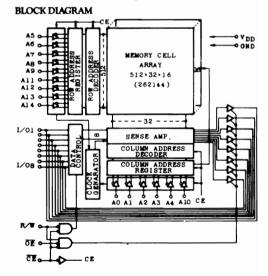

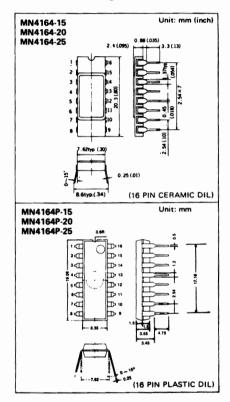

| 4164           | 64K x 1 Bit Dynamic RAM   | 590      |

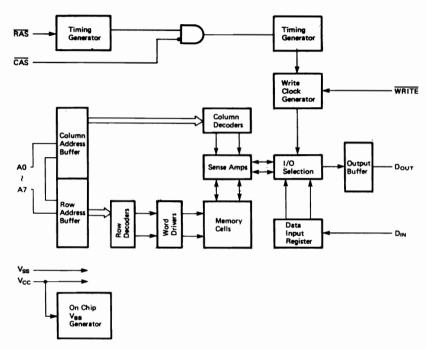

| 41256          | 256K x 1 Bit Dynamic RAM  | 592      |

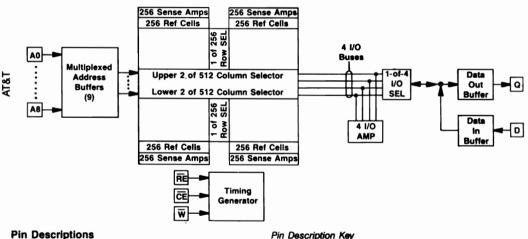

| 6256           | 256K x 1 Bit Dynamic RAM  | 593      |

| 511000         | IMB Dynamic RAM           | 594      |

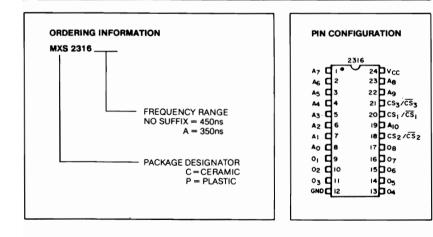

| 2316           | 2K x 8 Bit ROM            | 595      |

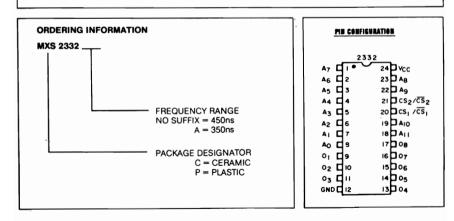

| 2332           | 4K x 8 Bit ROM            | 596      |

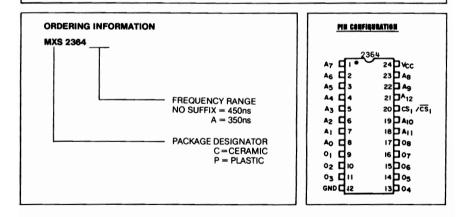

| 2334           | 8K x 8 Bit ROM            | 597      |

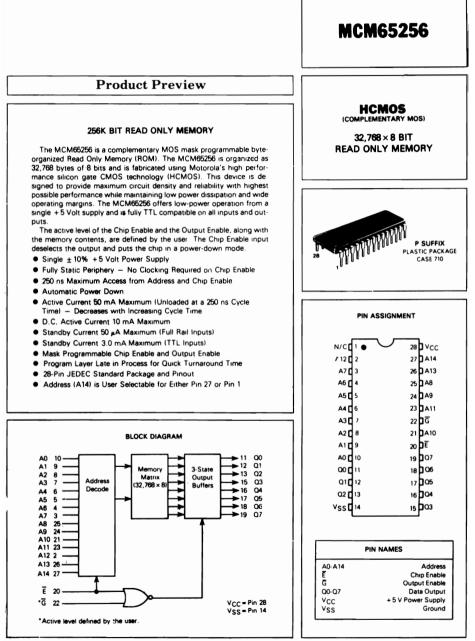

| 65256          | 32K x 8 Bit ROM           | 598      |

| 23512          | 64K x 8 Bit ROM           | 599      |

| 531000         | 128K x 8 Bit ROM          | 600      |

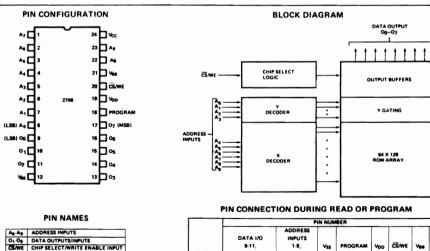

| 2708           | 1K x 8 Bit EPROM          | 601      |

| 2716           | 2K x 8 Bit EPROM          | 602      |

| 2732           | 4K x 8 Bit EPROM          | 604      |

| 2764           | 8K x 8 Bit EPROM          | 605      |

| 2816           | 2K x 8 Bit EPROM          | 606      |

| 27128          | 16K x 8 Bit EPROM         | 607      |

| 27256          | 32K x 8 Bit EPROM         | 608      |

| 27512          | 64K x 8 Bit EPROM         | 610      |

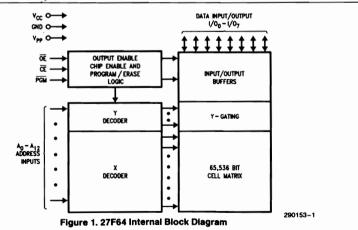

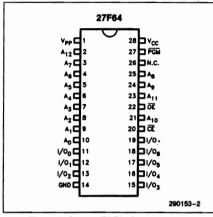

| 27F64          | 8K x 8 Bit Flash Memory   | 612      |

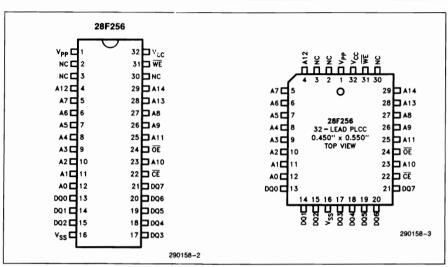

| 28F256         | 32K x 8 Bit Flash Memory  | 614      |

| 571000         | 128K x 8 Bit EPROM        | 616      |

| ANALOG DEVICES |                           |          |

| ADC0800        | 8 Bit A/D Convertor       | 617      |

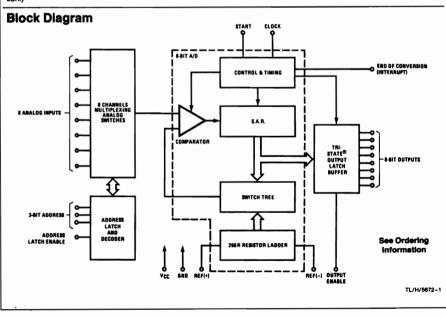

| ADC0808        | 8 Bit A/D Convertor       | 618      |

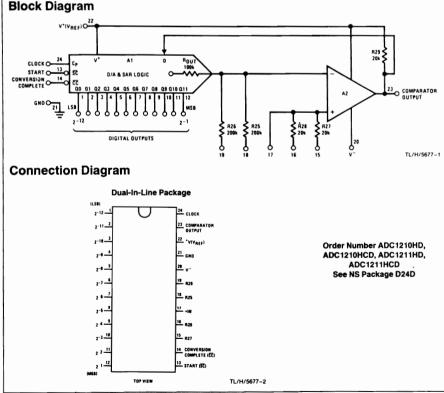

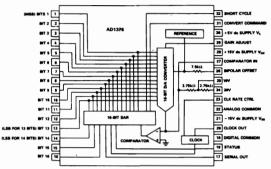

| AD1210         | 12 Bit A/D Convertor      | 619      |

| DAC0800        | 8 Bit D/A Convertor       | 620      |

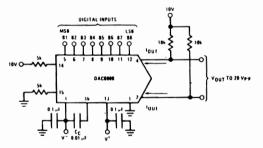

| DAC0808        | 8Bit D/A Convertor        | 621      |

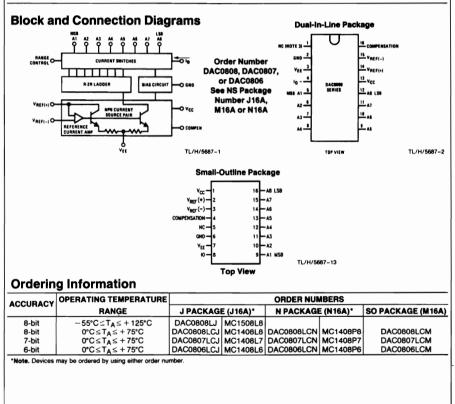

| DAC1210        | 12 Bit D/A Convertor      | 622      |

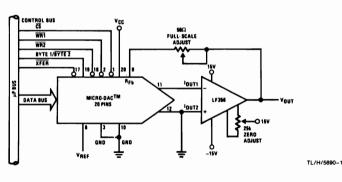

| AD568          | 12 Bit D/A Convertor      | 623      |

| AD664          | 12 Bit Quad DAC           | 624      |

| AD674          | 12 Bit A/D Convertor      | 625      |

| AD1376         | 16 Bit A/D Convertor      | 626      |

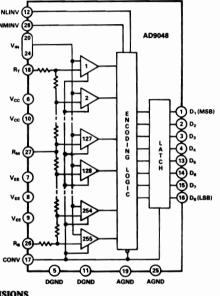

| AD9048         | 8 Bit Video A/D Convertor | 627      |

|                |                           |          |

### DEVICE NO. DEVICE FUNCTION

### PAGE NO.

### LINEAR I.C.s 7 op Amps

| LM311   | Voltage Comparator                  | 628 |

|---------|-------------------------------------|-----|

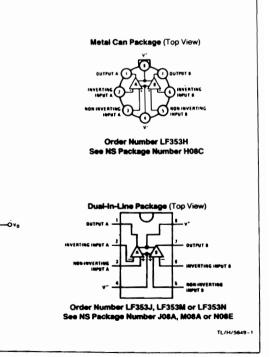

| LM353   | Operational Amplifier               | 629 |

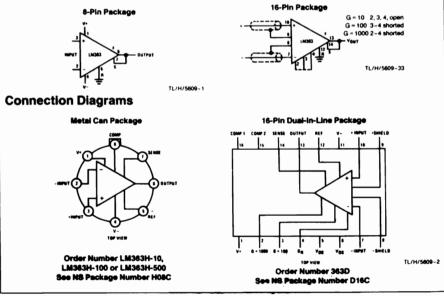

| LM363   | Precision Instrumentation Amplifier | 630 |

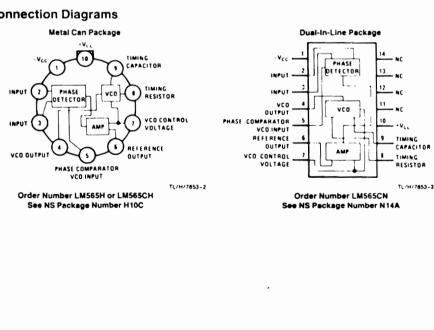

| LM565   | Phase Locked Loop                   | 631 |

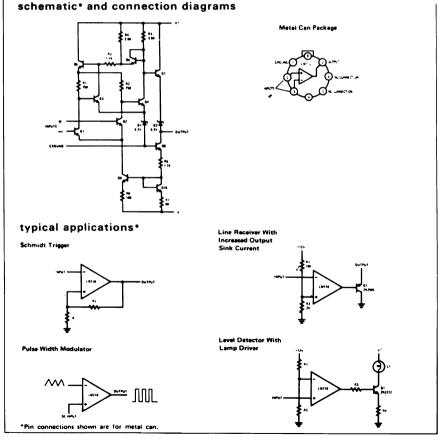

| LM710   | Voltage Comparator                  | 632 |

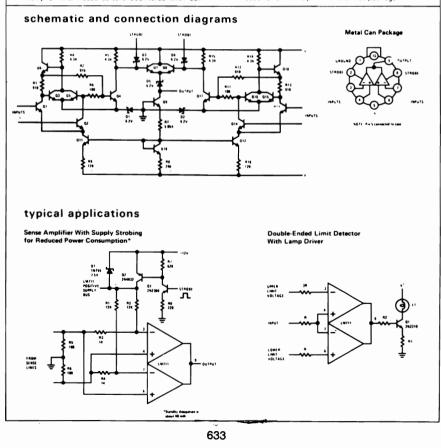

| LM711   | Dual Comparator                     | 633 |

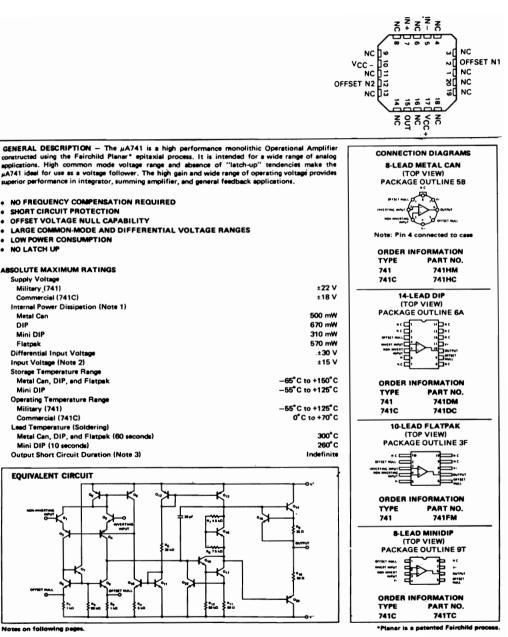

| uA741   | General Purpose op Amp.             | 634 |

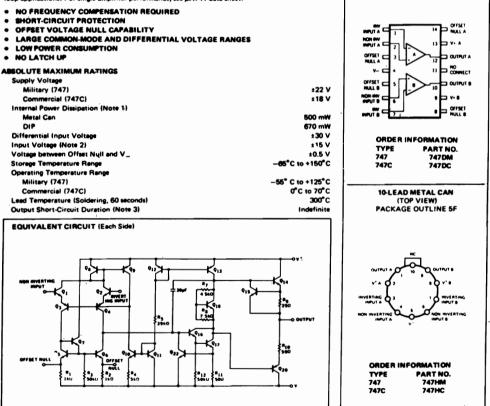

| uA747   | Dual op Amp.                        | 635 |

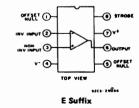

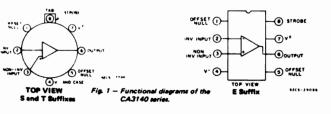

| CA 3130 | Operational Amplifier               | 636 |

| CA31340 | Operational Amplifier               | 637 |

### CLOCK CALCULATOR CHIPs

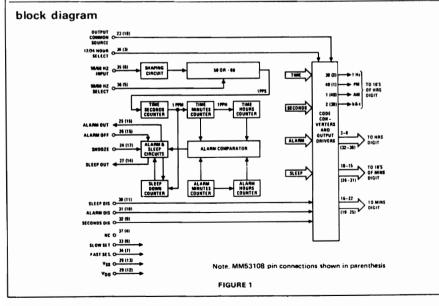

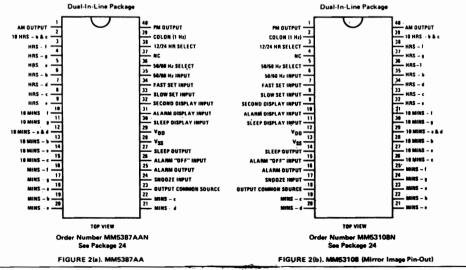

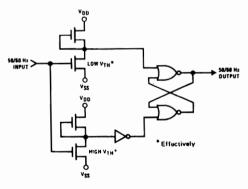

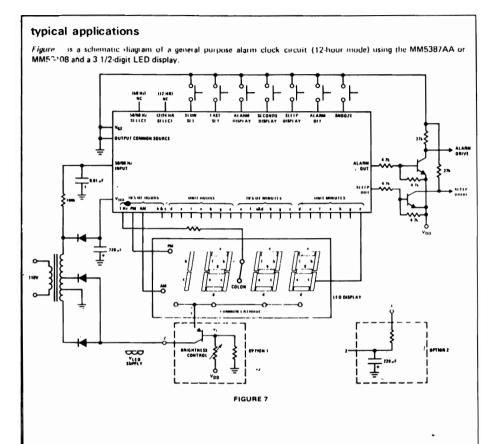

| MM5387  | Digital Alarm Clock                | 638 |

|---------|------------------------------------|-----|

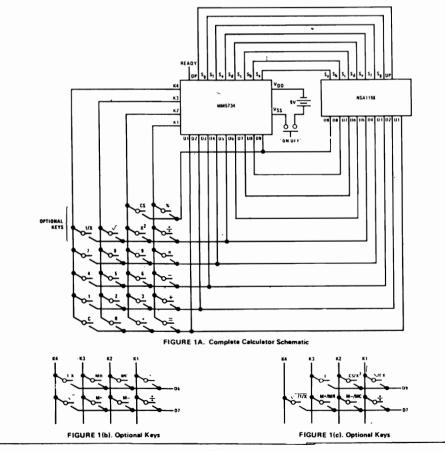

| MM5734  | 8-function Calculator              | 643 |

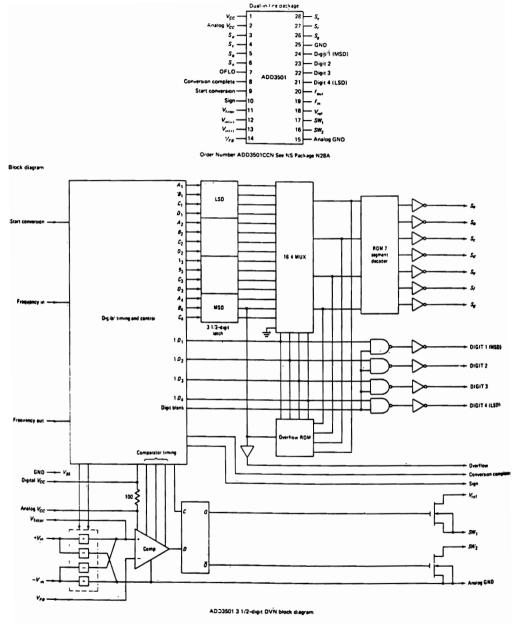

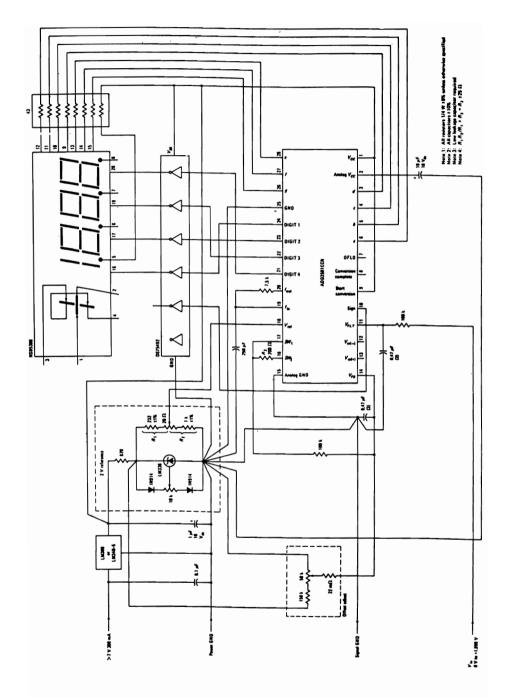

| ADC3501 | Digital Volt Meter                 | 646 |

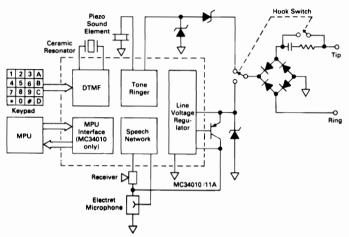

| MC34010 | Complete Electronic Telephone ckt. | 648 |

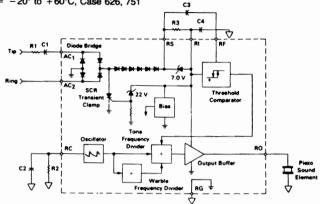

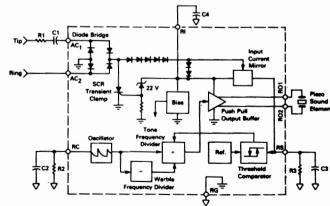

| MC34012 | Tone Ringer                        | 649 |

| PCF8200 | Male/Female Speech Synthesizer     | 650 |

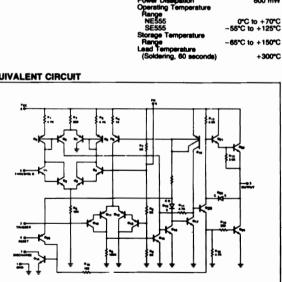

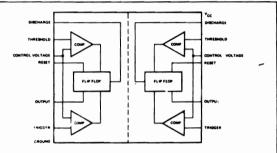

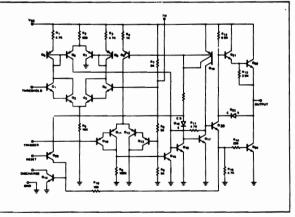

| 555     | Timer                              | 651 |

| 556     | Dual Timer                         | 652 |

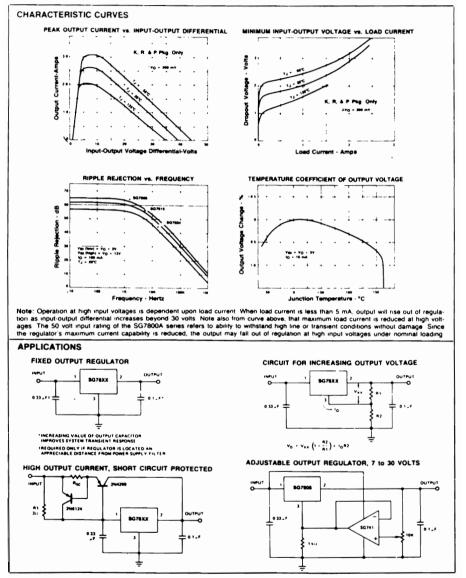

### VOLTAGE REGULATOR CHIPs

| 7800 series | 5, 8, 12, 24 Voltage Regulators    | 653 |

|-------------|------------------------------------|-----|

| SG123       | 3 Amp, 5V Positive Regulator       | 655 |

| SG723       | General Purpose Positive Regulator | 656 |

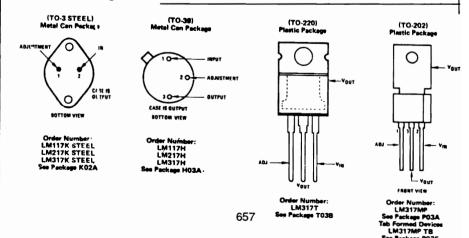

| LM317       | 3-Terminal Adjustable Regulator    | 657 |

| SG3524      | SMPS Control Circuit               | 658 |

|             | Standard Digital Bus Interface     | 659 |

|             | IEE488 Parallel Transmission       | 660 |

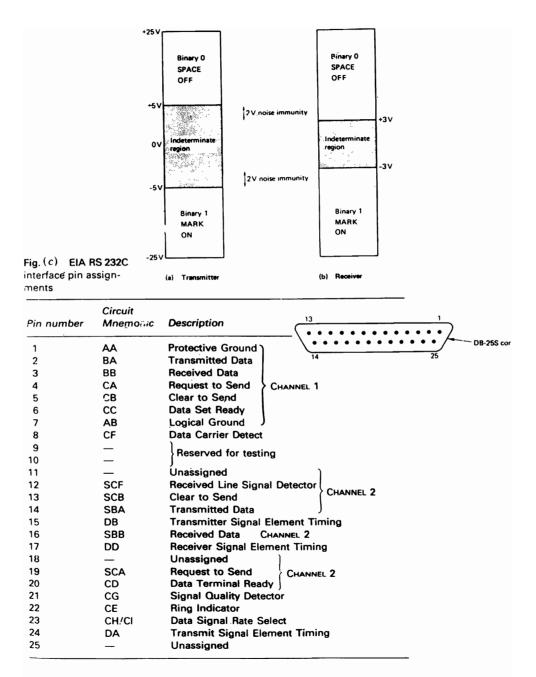

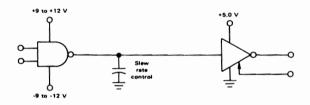

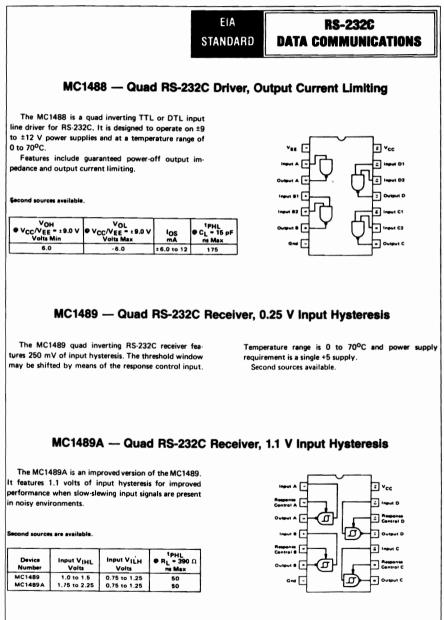

|             | EIA RS 232C Serial Transmission    | 662 |

|             | ASCII Code Chart                   | 666 |

|             | Number Conversion Table            | 667 |

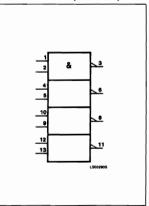

## 7400, LS00, S00 Gates

Quad Two-Input NAND Gate Product Specification

Logic Products

FUNCTION TABLE

A

L

L

н

н

H = HIGH voltage level L = LOW voltage level

INPUTS

в

L

н

L

н

| TYPE   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7400   | 9ns                          | 8mA                               |

| 74LS00 | 9.5ns                        | 1.6mA                             |

| 74S00  | 3ns                          | 15mA                              |

#### ORDERING CODE

| PACKAGES COMMERCIAL RANGE<br>V <sub>CC</sub> = 5V ±5%; T <sub>A</sub> = 0°C to +70°C |                           |  |

|--------------------------------------------------------------------------------------|---------------------------|--|

| Plastic DIP                                                                          | N7400N, N74LS00N, N74S00N |  |

| Plastic SO                                                                           | N74LS00D, N74S00D         |  |

#### NOTE:

OUTPUT

Y

н

н

·Η

L

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74S   | 74LS   |

|------|-------------|------|-------|--------|

| A, B | Inputs      | 1ul  | 1Sul  | 1LSul  |

| Y    | Output      | 10ul | 10Sul | 10LSul |

NOTE:

Where a 74 unit load (ul) is understood to be 40 $\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, a 74S unit load (Sul) is 50 $\mu$ A I<sub>IH</sub> and -2.0mA I<sub>IL</sub>, and 74LS unit load (LSul) is 20 $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

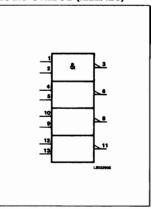

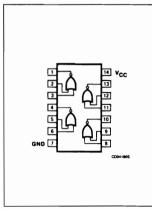

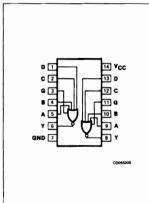

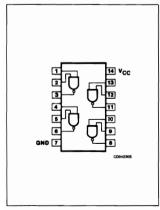

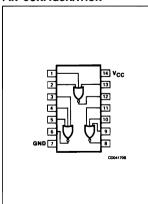

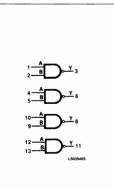

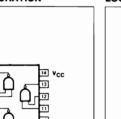

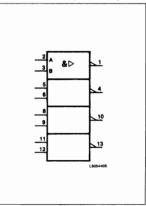

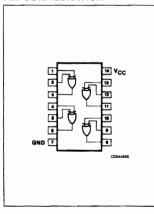

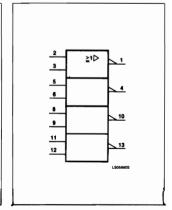

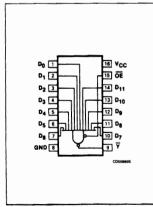

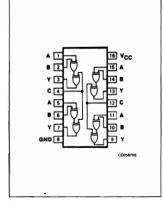

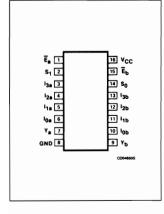

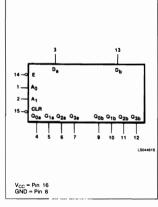

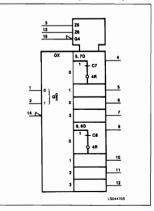

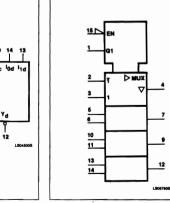

#### PIN CONFIGURATION

# 74LS01 Gate

Quad Two-Input NAND Gate (Open Collector) Product Specification

TYPE

TYPICAL PROPAGATION DELAY

TYPICAL SUPPLY CURRENT (TOTAL)

74LS01

16ns

1.6mA

#### **ORDERING CODE**

| PACKAGES    | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-------------|---------------------------------------------------------------------------|

| Plastic DIP | N74LS01N                                                                  |

| Plastic SO  | N74LS01D                                                                  |

#### FUNCTION TABLE

Logic Products

| INPUTS |     | OUTPUT |

|--------|-----|--------|

| A      | В   | Y      |

| L      | L   | н      |

| L      | н   | н      |

| н      | L L | н      |

| н      | н   | L      |

H = HIGH voltage level

L = LOW voltage level

### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74LS   |

|------|-------------|--------|

| A, B | Inputs      | 1LSui  |

| Y    | Output      | 10LSul |

NOTE:

Where a 74LS unit load (LSul) is  $20\mu$ A l<sub>IH</sub> and -0.4mA l<sub>IL</sub>.

#### PIN CONFIGURATION

## 7402, LS02, S02 Gates

Quad Two-Input NOR Gate Product Specification

TYPE

TYPICAL PROPAGATION DELAY

TYPICAL SUPPLY CURRENT (TOTAL)

7402

10ns

11mA

74LS02

10ns

2.2mA

74S02

3.5ns

22mA

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|----------------------------------------------------------------------------------|

| Plastic DIP | N7402N, N74LS02N, N74S02N                                                        |

| Plastic SO  | N74LS02D, N74S02D                                                                |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

### FUNCTION TABLE

| INPUTS |   | OUTPUT |

|--------|---|--------|

| A B    |   | Y      |

| L      | L | н      |

| L      | н | L      |

| н      | L | L      |

| н      | н | L      |

H = HIGH voltage level

L = LOW voltage level

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74S   | 74LS   |

|------|-------------|------|-------|--------|

| A, B | Inputs      | 1ul  | 1Sul  | 1LSul  |

| Y    | Output      | 10ul | 10Sul | 10LSul |

NOTE:

Where a 74 unit load (ul) is understood to be 40 $\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, a 74S unit load (Sul) is 50 $\mu$ A I<sub>IH</sub> and -2.0mA I<sub>IL</sub>, and 74LS unit load (LSul) is 20 $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

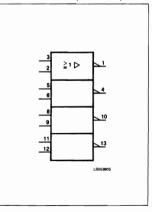

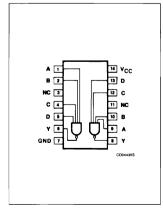

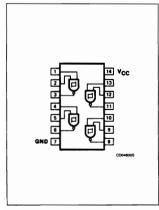

#### PIN CONFIGURATION

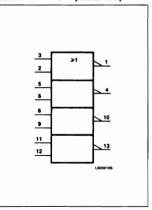

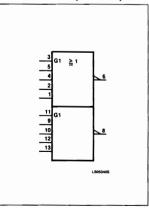

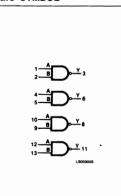

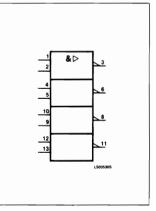

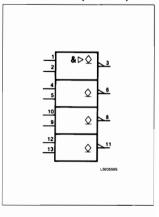

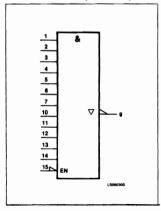

#### LOGIC SYMBOL (IEEE/IEC)

#### Logic Products

## 7403, S03 Gates

Quad Two-Input NAND Gate (Open Collector) Product Specification

Logic Products

FUNCTION TABLE

A

L

н

н

H = HIGH voltage level L = LOW voltage level

INPUTS

в

L

н

L H

| ТҮРЕ  | TYPICAL PROPAGATION<br>DELAY                         | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|-------|------------------------------------------------------|-----------------------------------|

| 7403  | 35ns (t <sub>PLH</sub> )<br>8ns (t <sub>PHL</sub> )  | 8mA                               |

| 74S03 | 5ns (t <sub>PLH</sub> )<br>4.5ns (t <sub>PHL</sub> ) | 13mA                              |

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-------------|---------------------------------------------------------------------------|

| Plastic DIP | N7403N, N74S03N                                                           |

| Plastic SO  | N74S03D                                                                   |

NOTE:

OUTPUT

Y

н

H H

L

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74S   |

|------|-------------|------|-------|

| А, В | Inputs      | 1ul  | 1Sul  |

| Y    | Output      | 10ul | 10Sul |

NOTE:

Where a 74 unit load (ul) is understood to be 40 $\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, a 74S unit load (Sul) is 50 $\mu$ A I<sub>IH</sub> and -2.0mA I<sub>IL</sub>.

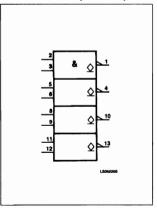

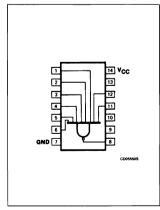

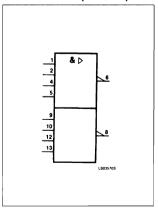

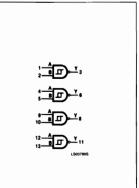

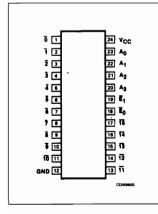

#### PIN CONFIGURATION

13

#### LOGIC SYMBOL (IEEE/IEC)

<u>¥</u> 11

## 7404, LS04, S04 Inverters

Hex Inverter Product Specification

#### **Logic Products**

| TYPE   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7404   | 10ns                         | 12mA                              |

| 74LS04 | 9.5ns                        | 2.4mA                             |

| 74S04  | 3ns                          | 22mA                              |

#### **ORDERING CODE**

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|-------------------------------------------------------------------------------|

| Plastic DIP | N7404N, N74LS04N, N74S04N                                                     |

| Plastic SO  | N74LS04D, N74S04D                                                             |

| NOTE:       |                                                                               |

For information regarding devices processed to Military Specifications, see the Signetics Military Products

ТИЧТИО ТЙЧИІ А А У Ц Н Н Ц

H = HIGH voltage level

FUNCTION TABLE

L = LOW voltage level

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74S   | 74LS   |

|------|-------------|------|-------|--------|

| A    | Input       | 1ul  | 1Sul  | 1LSul  |

| Y    | Output      | 10ul | 10Sul | 10LSul |

NOTE:

Data Manual.

Where a 74 unit load (ul) is understood to be 40µA I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, a 74S unit load (Sul) is 50µA I<sub>IH</sub> and -2.0mA I<sub>IL</sub>, and 74LS unit load (LSul) is 20µA I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

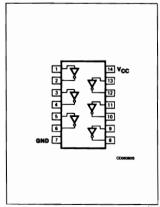

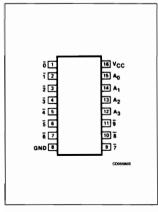

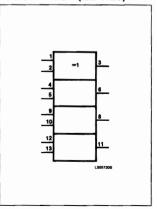

#### PIN CONFIGURATION

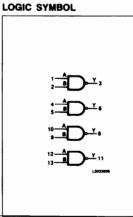

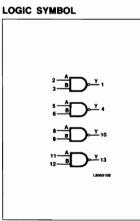

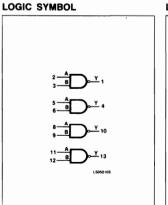

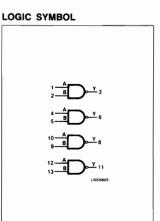

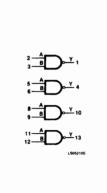

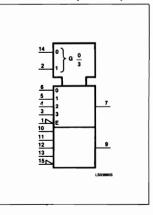

### LOGIC SYMBOL

## 7405, LS05, S05 Inverters

#### Hex Inverter (Open Collector) Product Specification

Logic Products

FUNCTION TABLE

A

L

н

H = HIGH voltage level L = LOW voltage level

| TYPE   | TYPICAL PROPAGATION<br>DELAY                         | TYPICAL SUPPLY CURRENT<br>(TOTAL) |  |

|--------|------------------------------------------------------|-----------------------------------|--|

| 7405   | 40ns (t <sub>PLH</sub> )<br>8ns (t <sub>PHL</sub> )  | 12mA                              |  |

| 74LS05 | 17ns (t <sub>PLH</sub> )<br>15ns (t <sub>PHL</sub> ) | 2.4mA                             |  |

| 74S05  | 5ns (t <sub>PLH</sub> )<br>4.5ns (t <sub>PHL</sub> ) | 20mA                              |  |

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|-------------------------------------------------------------------------------|

| Plastic DIP | N7405N, N74LS05N, N74S05N                                                     |

| Plastic SO  | N74LS05D, N74S05D                                                             |

| Ceramic DIP |                                                                               |

#### NOTE:

OUTPUT

Y

н

L

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 745   | 74LS   |

|------|-------------|------|-------|--------|

| A    | Input       | 1ul  | 1Sul  | 1LSul  |

| Y    | Output      | 10ul | 10Sul | 10LSul |

| ·    |             |      |       |        |

NOTE:

Where a 74 unit load (ul) is understood to be 40 $\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, a 74S unit load (Sul) is 50 $\mu$ A I<sub>IH</sub> and -2.0mA I<sub>IL</sub>, and 74LS unit load (LSul) is 20 $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

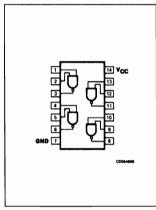

#### **PIN CONFIGURATION**

#### LOGIC SYMBOL

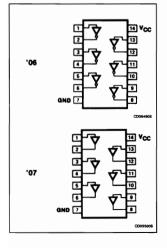

## 7406, 07 Inverter/Buffer/Drivers

'06 Hex Inverter Buffer/Driver (Open Collector)

'07 Hex Buffer/Driver (Open Collector)

Product Specification

Logic Products

| TYPE | TYPICAL PROPAGATION<br>DELAY                         | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|------|------------------------------------------------------|-----------------------------------|

| 7406 | 10ns (t <sub>PLH</sub> )<br>15ns (t <sub>PHL</sub> ) | 31mA                              |

| 7407 | 6ns (t <sub>PLH</sub> )<br>20ns (t <sub>PHL</sub> )  | 25mA                              |

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-------------|------------------------------------------------------------------------|

| Plastic DIP | N7406N, N7407N                                                         |

| Plastic SO  | N7406D, N7407D                                                         |

For information regarding devices processed to Military Specifications, see the Signetics Military Products

#### FUNCTION TABLE

| '06   |        | '07   |        |

|-------|--------|-------|--------|

| INPUT | OUTPUT | INPUT | OUTPUT |

| A     | Y      | A     | Y      |

| н     | L      | н     | н      |

| L     | н      | L     | L      |

| INPUT AND OUTPUT LOADING AND FAN-OUT TABLE |             |      |  |  |

|--------------------------------------------|-------------|------|--|--|

| PINS                                       | DESCRIPTION | 74   |  |  |

| A                                          | Input       | 1ul  |  |  |

| Y                                          | Output      | 10ul |  |  |

H = HIGH voltage level L = LOW voltage level

NOTE:

Data Manual.

Where a 74 unit load (ul) is understood to be  $40\mu A I_{IH}$  and -1.6mA I<sub>IL</sub>.

#### PIN CONFIGURATION

### LOGIC SYMBOL

## 7408, LS08, S08 Gates

Quad Two-Input AND Gate Product Specification

Logic Products

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7408   | 15ns                         | 16mA                              |

| 74LS08 | 9ns                          | 3.4mA                             |

| 74S08  | 5ns                          | 25mA                              |

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|----------------------------------------------------------------------------------|

| Plastic DIP | N7408N, N74LS08N, N74S08N                                                        |

| Plastic SO  | N74LS08N, N74S08N                                                                |

|             |                                                                                  |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

## FUNCTION TABLE

| INPUTS |   | OUTPUT |

|--------|---|--------|

| •      | В | Y      |

| L      | L | L      |

| L      | н | ι      |

| н      | L | ι      |

| н      | н | н      |

H = HIGH voltage level L = LOW voltage level

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 7 <b>4</b> S | 74LS   |

|------|-------------|------|--------------|--------|

| A, B | Inputs      | 1ui  | 1Sul         | 1LSul  |

| Y    | Output      | 10ul | 10Sul        | 10LSul |

NOTE:

Where a 74 unit load (ul) is understood to be 40  $\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, a 74S unit load (Sul) is 50  $\mu$ A I<sub>IH</sub> and -2.0mA I<sub>IL</sub>, and 74LS unit load (LSul) is 20  $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

#### PIN CONFIGURATION

# 74LS09 Gates

Quad Two-Input AND Gate (Open Collector) Product Specification

#### Logic Preducts

| TYPE   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 74LS09 | 23ns                         | 4.3                               |

#### **ORDERING CODE**

| PACKAGES    | $\begin{array}{c} \text{COMMERCIAL RANGE} \\ \text{V}_{\text{CC}} = 5\text{V} \pm 5\text{\%}; \ \text{T}_{\text{A}} = 0^{\circ}\text{C} \ \text{to} \ +70^{\circ}\text{C} \end{array}$ |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Plastic DIP | N74LS09N                                                                                                                                                                               |

NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### FUNCTION TABLE

| INPUTS |   | OUTPUT |

|--------|---|--------|

| A      | В | Y      |

| L      | L | L      |

| L      | н | L      |

| н      | L | L      |

| н      | н | н      |

H = HIGH voltage level

L = LOW voltage level

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74LS   |

|------|-------------|--------|

| A, B | Inputs      | 1LSul  |

| Y    | Output      | 10LSui |

NOTE:

Where 74LS unit load (LSul) is 20µA IIH and -0.4mA IIL.

#### Logic Products

FUNCTION TABLE

H

L

н

INPUTS

L н н L

H = HIGH voltage level L = LOW voltage level

A в С

L L L

L L

L н

L н н

н L L

н

н н н OUTPUTS

Y('11)

L

L

L

L

L

L

L

н

Y('10)

н

н

н

н

н

н

н

L

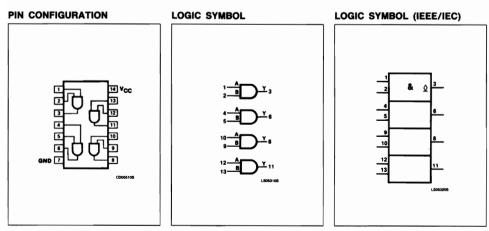

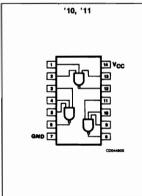

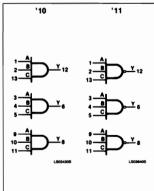

## 7410, 7411, LS10, LS11, S10, S11 Gates

#### Triple Three-Input NAND ('10), AND ('11) Gates **Product Specification**

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7410   | 9ns                          | 6mA                               |

| 74LS10 | 10ns                         | 1.2mA                             |

| 74S10  | 3nis                         | 12mA                              |

| 7411   | 10ns                         | 11mA                              |

| 74LS11 | 9ns                          | 2.6mA                             |

| 74S11  | 5ns                          | 19mA                              |

#### **ORDERING CODE**

| PACKAGES        | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-----------------|---------------------------------------------------------------------------|

| Plastic DIP '10 | N7410N, N74LS10N, N74S10N                                                 |

| '11             | N7411N, N74LS11N, N74S11N                                                 |

| Plastic SO '10  | N74LS10D, N74S10D                                                         |

| Plastic SO '11  | N74LS11D, N74S11D                                                         |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74S   | 74LS   |

|------|-------------|------|-------|--------|

| A-C  | Inputs      | 1ul  | 1Sul  | 1LSul  |

| Y    | Output      | 10ul | 10Sul | 10LSul |

NOTE:

Where a 74 unit load (ul) is understood to be  $40\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, a 74S unit load (Sul) is  $50\mu$ A I<sub>IH</sub> and -2.0mA IIL, and 74LS unit load (LSul) is 20µA IIH and -0.4mA IIL.

### PIN CONFIGURATION

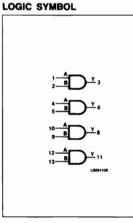

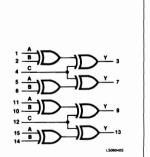

#### LOGIC SYMBOL

|                                       | т          | 54/741<br>RIPLE 3-INPUT N<br>(With Open-Collec                            | AND GATE                                                                    |       |            | ON DIAGRAM<br>DUT A |

|---------------------------------------|------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|------------|---------------------|

| ORDERIN                               | T          | E: See Section 9<br>COMMERCIAL GRADE                                      | MILITARY GRADE                                                              |       |            |                     |

| PKGS                                  | PIN<br>OUT | $V_{CC} = +5.0 V \pm 5\%,$<br>$T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ | $V_{CC} = +5.0 V \pm 10\%$<br>$T_A = -55^{\circ}C \text{ to } +125^{\circ}$ |       |            |                     |

| Plastic<br>DIP (P)                    | A          | 7412PC                                                                    |                                                                             | 9A    |            |                     |

| Ceramic<br>DIP (D)                    | A          | 7412DC                                                                    | 5412DM                                                                      | 6A    |            |                     |

| Flatpak<br>(F)                        | •          | 7412FC                                                                    | 5412FM                                                                      | 31    |            |                     |

| INPUT LO<br>PINS<br>Inputs<br>Outputs | ADING      | /FAN-OUT: See Section 3<br>54/74 (U.L.)<br>HIGH/LOW<br>1.0/1.0<br>OC**/10 | for U.L. definitions                                                        |       |            |                     |

| DC AND                                |            | RACTERISTICS: See Sec                                                     | tion 3*                                                                     |       |            |                     |

| SYMBOL                                |            | PARAMETER                                                                 | 54/74<br>Min Max                                                            | UNITS | COND       |                     |

|                                       | <u> </u>   |                                                                           | 6.0                                                                         | mA    | VIN = Gnd  | Vcc = Max           |

| ICCH<br>ICCL                          | Powe       | r Supply Current                                                          | 16.5                                                                        |       | VIN = Open |                     |

#### Logic Products

#### DESCRIPTION

The '13 contains two 4-input NAND gates which accept standard TTL input signals and provide standard TTL output levels. They are capable of transforming slowly changing input signals into sharply defined, jitter-free output signals. In addition, they have greater noise margin than conventional NAND gates.

Each circuit contains a 4-input Schmitt trigger followed by a Darlington level shifter and a phase splitter driving a TTL totem-pole output. The Schmitt trigger uses positive feedback to effectively speed-up slow input transitions, and provide different input threshold voltages for positive and negative-going transitions. This hysteresis between the positive-going and negative-going input threshold (typically 800mV) is determined by resistor ratios and is essentially insensitive to temperature and supply voltage variations. As long as three inputs remain at a more positive voltage than Vt+ MAX, the gate will respond in the transitions of the other input as shown in Waveform 1.

## 7413, LS13 Gates

Dual 4-Input NAND Schmitt Trigger Product Specification

| TYPE   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7413   | 17ns                         | 17mA                              |

| 74LS13 | 17ns                         | 3.5mA                             |

#### **ORDERING CODE**

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-------------|------------------------------------------------------------------------|

| Plastic DIP | N7413N, N74LS13N                                                       |

NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74LS   |

|------|-------------|------|--------|

| All  | Inputs      | 1ul  | 1LSul  |

| Y    | Output      | 10ul | 10LSul |

#### NOTE:

Where a 74 unit load (ul) is understood to be 40 $\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, and 74LS unit load (LSul) is 20 $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

**PIN CONFIGURATION**

#### Logic Products

#### DESCRIPTION

The '14 contains six logic inverters which accept standard TTL input signals and provide standard TTL output levels. They are capable of transforming slowly changing input signals into sharply defined, jitter-free output signals. In addition, they have greater noise margin than conventional inverters.

Each circuit contains a Schmitt trigger followed by a Darlington level shifter and a phase splitter driving a TTL totem-pole output. The Schmitt trigger uses positive feedback to effectively speed-up slow input transition, and provide different input threshold voltages for positive and negative-going transitions. This hysteresis between the positive-going and negative-going input thresholds (typically 800mV) is determined internally by resistor ratios and is essentially insensitive to temperature and supply voltage variations.

## 7414, LS14 Schmitt Triggers

Hex Inverter Schmitt Trigger Product Specification

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7414   | 15ns                         | 31mA                              |

| 74LS14 | 15ns                         | 10mA                              |

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|-------------------------------------------------------------------------------|

| Plastic DIP | N7414N, N74LS14N                                                              |

| Plastic SO  | N74LS14D                                                                      |

#### NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74LS   |

|------|-------------|------|--------|

| A    | Inputs      | 1ul  | 1LSul  |

| Y    | Output      | 10ul | 10LSul |

#### NOTE:

Where a 74 unit load (ui) is understood to be 40 $\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, and 74LS unit load (LSuI) is 20 $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

#### **PIN CONFIGURATION**

#### LOGIC SYMBOL

×.

A 0 12

|                                                                                                |            |                                                                                      |                                     |                                                                |             | CONNECTION<br>PINOU  |                    |

|------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------|-------------|----------------------|--------------------|

|                                                                                                |            | 54S/74S<br>54LS/74L<br>RIPLE 3-INPUT A<br>(With Open-Collector<br>E: See Section 9   | S15<br>AND GA                       | · —                                                            |             | ~                    | Τυνα               |

| UNDENIN                                                                                        |            |                                                                                      | MILITAR                             | GRADE                                                          |             | <u>و</u>             | ╟╌┢┓               |

| PKGS                                                                                           | PIN<br>OUT | $V_{CC} = +5.0 V \pm 5\%,$<br>$T_A = 0^{\circ}C \text{ to } +70^{\circ}C$            |                                     | 0 V ±10%,                                                      | PKG<br>TYPE | 3                    |                    |

| Plastic<br>DIP (P)                                                                             | A          | 74S15PC, 74LS15PC                                                                    |                                     |                                                                | 9A          | 5                    |                    |

| Ceramic<br>DIP (D)                                                                             | A          | 74S15DC, 74LS15DC                                                                    | 54S15DM, 5                          | 4LS15DM                                                        | 6A          |                      | ·ī                 |

| Flatpak<br>(F)                                                                                 | A          | 74S15FC, 74LS15FC                                                                    | 54S15FM, 54                         | LS15FM                                                         | 31          |                      |                    |

| INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions<br>PINS 54/748 (U.L.) 54/74LS (U.L.) |            |                                                                                      |                                     |                                                                |             |                      |                    |

| PINS                                                                                           |            |                                                                                      |                                     |                                                                |             |                      |                    |

| PINS<br>Inputs<br>Outputs                                                                      |            | 54/748 (U.L.)<br>HIGH/LOW<br>1.25/1.25<br>OC**/12.5                                  | н                                   | 74LS (U.L.)<br>IGH/LOW<br>0.5/0.25<br>OC**/5.0<br>(2.5)        |             |                      |                    |

| Inputs<br>Outputs                                                                              | ас сн      | HIGH/LOW<br>1.25/1.25                                                                | н                                   | IGH/LOW<br>0.5/0.25<br>OC**/5.0                                |             |                      |                    |

| Inputs<br>Outputs                                                                              | ас сн      | HIGH/LOW<br>1.25/1.25<br>OC**/12.5                                                   | H<br>ection 3*<br>54/748            | IGH/LOW<br>0.5/0.25<br>OC**/5.0<br>(2.5)<br>54/74LS            | UNITS       | CONDIT               | TONS               |

| Inputs<br>Outputs<br>DC AND                                                                    |            | HIGH/LOW<br>1.25/1.25<br>OC**/12.5<br>ARACTERISTICS: See Se                          | H<br>ection 3*                      | IGH/LOW<br>0.5/0.25<br>OC**/5.0<br>(2.5)<br>54/74LS            | UNITS       | CONDIT<br>Vin = Open |                    |

| Inputs<br>Outputs<br>DC AND<br>SYMBOL                                                          |            | HIGH/LOW<br>1.25/1.25<br>OC**/12.5<br>ARACTERISTICS: See So<br>PARAMETER<br>r Supply | H<br>ection 3*<br>54/748<br>Min Max | IGH/LOW<br>0.5/0.25<br>0C**/5.0<br>(2.5)<br>54/74LS<br>Min Max |             |                      | TIONS<br>Vcc = Max |

\*DC limits apply over operating temperature range; AC limits apply at  $T_A$  = +25\*C and V<sub>CC</sub> = +5.0 V.

"OC-Open Collector

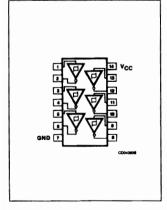

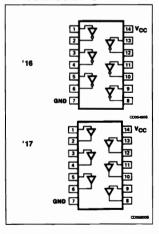

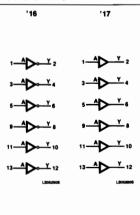

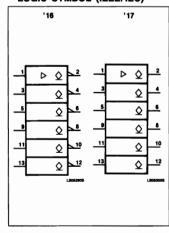

## 7416, 17 Inverter/Buffer/Drivers

'16 Hex Inverter Buffer/Driver (Open Collector)

'17 Hex Buffer/Driver (Open Collector)

Product Specification

### Logic Products

| TYPE | TYPICAL PROPAGATION<br>DELAY                         | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|------|------------------------------------------------------|-----------------------------------|

| 7416 | 10ns (t <sub>PLH</sub> )<br>15ns (t <sub>PHL</sub> ) | 31mA                              |

| 7417 | 6ns (t <sub>PLH</sub> )<br>20ns (t <sub>PHL</sub> )  | 25mA                              |

#### **ORDERING CODE**

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|-------------------------------------------------------------------------------|

| Plastic DIP | N7416N, N7417N                                                                |

| Plastic SO  | N7417D                                                                        |

#### NOTE:

'17

OUTPUT

Y

L

н

INPUT

A

L

н

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   |

|------|-------------|------|

| A    | Input       | 1ul  |

| Y    | Output      | 10ul |

|      |             |      |

NOTE:

A 74 unit load (ul) is understood to be 40µA IIH and -1.6mA IIL.

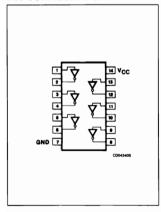

#### **PIN CONFIGURATION**

FUNCTION TABLE

'16

H = HIGH voltage level L = LOW voltage level

OUTPUT

Y

н

L

INPUT

A

L

н

#### LOGIC SYMBOL

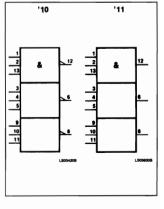

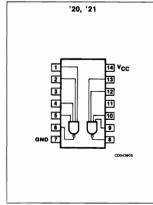

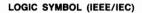

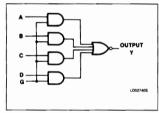

## 7420, 7421, LS20, LS21, S20 Gates

#### Logic Products

FUNCTION TABLE

INPUTS

XL

н н

н

H = HIGH voltage level L = LOW voltage level X = Don't care

A B C D

L X X X H

X | L | X | X

XXLXXX

x x

н

Dual Four-Input NAND ('20) AND ('21) Gate Product Specification

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7420   | 10ns                         | 8mA                               |

| 74LS20 | 10ns                         | 0.8mA                             |

| 74S20  | 3ns                          | 8mA                               |

| 7421   | 12ns                         | 8mA                               |

| 74LS21 | 9ns                          | 1.7mA                             |

#### ORDERING CODE

| PACKAGES           | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |  |

|--------------------|-------------------------------------------------------------------------------|--|

| Plastic DIP<br>'20 | N7420N, N74LS20N, N74S20N                                                     |  |

| '21                | N7421N, N74LS21N                                                              |  |

| Plastic SO         | N74LS20D, N74S20D, N74LS21D                                                   |  |

#### NOTE:

OUTPUTS

Y('21)

L

L

L

Ē

Ĥ

Y('20)

н

н

н

1

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS  | DESCRIPTION | 74   | 74S   | 74LS   |

|-------|-------------|------|-------|--------|

| A – D | Inputs      | 1ul  | 1Sul  | 1LSul  |

| Y     | Output      | 10ul | 10Sul | 10LSul |

#### NOTE:

Where a 74 unit load (ul) is understood to be 40 $\mu$ A I<sub>IH</sub> and -1.6mA I<sub>IL</sub> a 74S unit load (Sul) is 50 $\mu$ A I<sub>IH</sub> and -2.0mA I<sub>IL</sub>, and 74LS unit load (LSul) is 20 $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

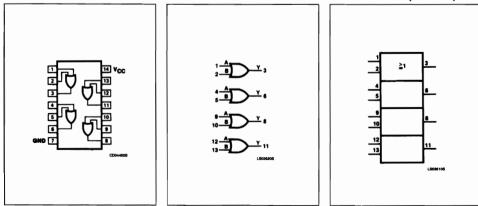

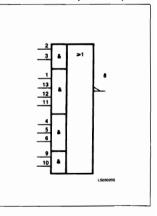

### PIN CONFIGURATION

#### LOGIC SYMBOL

20, 21

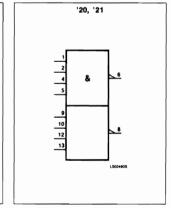

## 7425 Gate

**Dual Four-Input NOR Gate With Strobe Product Specification**

Logic Products

#### FUNCTION TABLE

|   | 1 | OUTPUT |   |   |   |

|---|---|--------|---|---|---|

| A | в | С      | D | G | Y |

| Х | X | X      | X | L | н |

| н | X | X      | X | н | L |

| x | н | X      | X | н | L |

| X | X | н      | X | н | L |

| X | X | X      | н | н | L |

| L | L | L      | L | н | н |

H = HIGH voltage level

L = LOW voltage level X = Don't care

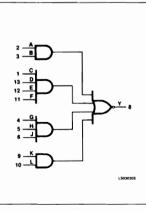

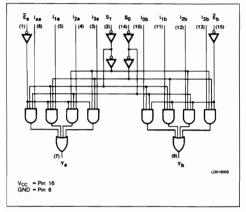

#### LOGIC DIAGRAM

#### TYPICAL PROPAGATION TYPICAL SUPPLY CURRENT TYPE DELAY (TOTAL) 7425 9ns 9mA

#### **ORDERING CODE**

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-------------|------------------------------------------------------------------------|

| Plastic DIP | N7425N                                                                 |

NOTE

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS  | DESCRIPTION | 74   |

|-------|-------------|------|

| A – D | Inputs      | 1ul  |

| G     | Input       | 4ul  |

| Y     | Output      | 10ul |

#### NOTE:

Where a 74 unit load (ul) is understood to be  $40\mu A I_{IH}$  and  $-1.6mA I_{IL}$ .

#### PIN CONFIGURATION

# 7426, LS26 Gates

Quad Two-Input NAND Gate (Open Collector) Product Specification

Logic Products

| TYPE   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7426   | 14ns                         | 8mA                               |

| 74LS26 | 16ns                         | 1.6mA                             |

#### **ORDERING CODE**

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-------------|------------------------------------------------------------------------|

| Plastic DIP | N7426N, N74LS26N                                                       |

| Plastic SO  | N74LS26D                                                               |

| IOTE:       |                                                                        |

#### FUNCTION TABLE

| INPUTS                                          |   | OUTPUT |  |

|-------------------------------------------------|---|--------|--|

| A                                               | В | Y      |  |

| L                                               | L | н      |  |

| L                                               | н | н      |  |

| н                                               | L | н      |  |

| н                                               | н | L      |  |

| H = HIGH voltage level<br>L = LOW voltage level |   |        |  |

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74  | 74LS   |

|------|-------------|-----|--------|

| A,B  | Inputs      | 1ul | 1LSul  |

| Y    | Y Output    |     | 10LSul |

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

NOTE:

Where a 74 unit load (uI) is understood to be 40  $\mu$  I<sub>IH</sub> and -1.6mA I<sub>IL</sub> and a 74LS unit load (LSuI) is 20  $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

#### PIN CONFIGURATION

#### LOGIC SYMBOL

#### LOGIC SYMBOL (IEEE/IEC)

4

# 7427, LS27 Gates

Triple Three-Input NOR Gate Product Specification

Logic Products

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7427   | 9ns                          | 13mA                              |

| 74LS27 | 10ns                         | 2.7mA                             |

### **ORDERING CODE**

| PACKAGES    | $\begin{array}{c} \mbox{COMMERCIAL RANGE} \\ \mbox{V}_{CC} = 5V \pm 5\%; \ \mbox{T}_{A} = 0^{\circ}\mbox{C} \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Plastic DIP | N7427N, N74LS27N                                                                                                                                   |

| Plastic SO  | N74LS27D                                                                                                                                           |

| NOTE:       |                                                                                                                                                    |

#### FUNCTION TABLE

| INPUTS |   |   | OUTPUT |

|--------|---|---|--------|

| A      | В | С | Y      |

| L      | L | L | н      |

| X      | X | н | L      |

| X      | н | X | L      |

| н      | × | x | L      |

### H = HIGH voltage level

L = LOW voltage level

X = Don't care

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74LS   |

|------|-------------|------|--------|

| A-C  | Inputs      | 1ul  | 1LSul  |

| Y    | Output      | 10ul | 10LSul |

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

NOTE:

Where a 74 unit load (ul) is understood to be  $40\mu A~l_{|H}$  and -1.6mA  $l_{|L}$  a 74LS unit load (LSul) is 20\muA  $l_{|H}$  and -0.4mA  $l_{|L}.$

#### PIN CONFIGURATION

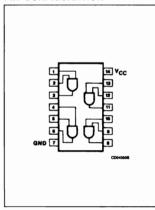

## 7428 Buffer

Quad Two-Input NOR Buffer Product Specification

Logic Products

| TYPE | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|------|------------------------------|-----------------------------------|

| 7428 | 7ns                          | 23mA                              |

#### ORDERING CODE

| PACKAGES           | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |  |

|--------------------|---------------------------------------------------------------------------|--|

| Plastic DIP N7428N |                                                                           |  |

NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

#### FUNCTION TABLE

| INPUTS |   | OUTPUT |

|--------|---|--------|

| A      | В | Y      |

| L      | L | н      |

| L      | н | L      |

| н      | L | L      |

| н      | н | L      |

| INPUT AND | OUTPUT | LOADING | AND   | FAN-OUT | TABLE |  |

|-----------|--------|---------|-------|---------|-------|--|

| DINC      |        | DEC     | ODIDT |         |       |  |

| PINS | DESCRIPTION | 74   |

|------|-------------|------|

| A, B | Inputs      | 1ul  |

| Y    | Output      | 30ul |

| NOTE |             |      |

NOTE: Where a 74 unit load (ui) is understood to be  $40\mu A$   $I_{IH}$  and -1.6mA  $I_{IL}.$

H = HIGH voltage level L = LOW voltage level

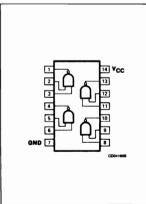

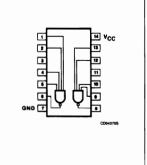

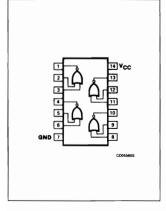

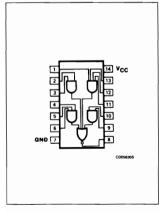

#### PIN CONFIGURATION

GND [

Vcc

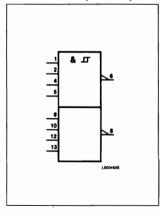

## 7430, LS30 Gates

**Eight-Input NAND Gate Product Specification**

#### Logic Products

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7430   | 11ns                         | 2mA                               |

| 74LS30 | 11ns                         | 0.5mA                             |

#### ORDERING CODE

PINS

A-H

Y

is  $20\mu A I_{IH}$  and  $-0.4mA I_{IL}$ .

NOTE:

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-------------|------------------------------------------------------------------------|

| Plastic DIP | N7430N, N74LS30N                                                       |

| Plastic SO  | N74LS30D                                                               |

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manuel.

Where a 74 unit load (ul) is understood to be  $40\mu A I_{IH}$  and -1.6mA  $I_{IL}$ , and a 74LS unit load (LSul)

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

DESCRIPTION

Inputs

Output

#### FUNCTION TABLE

|   | INPUTS |   |   |   |   |   | OUTPUT |   |

|---|--------|---|---|---|---|---|--------|---|

| A | в      | С | D | Е | F | G | н      | Y |

| L | X      | х | x | x | x | X | х      | н |

| X | L      | X | X | X | X | x | X      | н |

| X | X      | L | X | X | X | X | X      | н |

| X | X      | X | L | X | X | X | X      | н |

| X | X      | X | X | L | X | X | X      | н |

| X | X      | X | X | X | L | X | X      | н |

| X | X      | X | X | X | X | L | X      | н |

| X | X      | X | X | X | X | х | L      | н |

| н | н      | н | н | н | н | н | н      | L |

H = HIGH voltage level L = LOW voltage level

X = Don't care

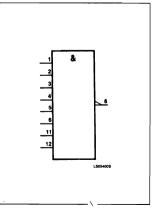

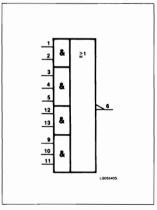

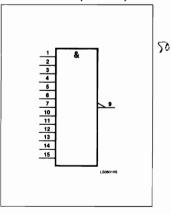

#### **PIN CONFIGURATION**

#### LOGIC SYMBOL (IEEE/IEC)

74

1ul

10ul

74LS

1LSul

10LSul

## 7432, LS32, S32 Gates

Quad Two-Input OR Gate Product Specification

Logic Products

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7432   | 12ns                         | 19mA                              |

| 74LS32 | 14ns                         | 4.0mA                             |

| 74S32  | 4ns                          | 28mA                              |

#### ORDERING CODE

| PACKAGES        | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 5\%$ ; T <sub>A</sub> = 0°C to +70°C |

|-----------------|---------------------------------------------------------------------------|

| Plastic DIP     | N7432N, N74LS32N, N74S32N                                                 |

| Plastic SO - 14 | N74LS32D, N74S32D                                                         |

#### NOTE: For information regarding devices processed to Military Specifications, see the Signetics Military Products

Data Manual.

FUNCTION TABLE

| INP | OUTPUT |   |

|-----|--------|---|

| A   | Y      |   |

| L   | L      | L |

| L   | н      | н |

| н   | L      | н |

| н   | н      | н |

H = HIGH voltage level

L = LOW voltage level

### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74S   | 74LS   |

|------|-------------|------|-------|--------|

| A, B | Inputs      | 1ul  | 1Sul  | 1LSul  |

| Y    | Output      | 10ul | 10Sul | 10LSul |

NOTE:

Where a 74 unit load (ul) is understood to be 40µA I<sub>|H</sub> and -1.6mA I<sub>|L</sub>, and a 74S unit load (Sul) is 50µA I<sub>|H</sub> and -2.0mA I<sub>|L</sub>, and a 74LS unit load (LSul) is 20µA I<sub>|H</sub> and -0.4mA I<sub>|L</sub>

#### **PIN CONFIGURATION**

#### LOGIC SYMBOL

## 7433, LS33 Buffers

Quad Two-Input NOR Buffer (Open Collector) Product Specification

#### Logic Products

| TYPE   | PE TYPICAL PROPAGATION TYPICAL SUPPLY C<br>DELAY (TOTAL) |      |

|--------|----------------------------------------------------------|------|

| 7433   | 11ns                                                     | 23mA |

| 74LS33 | 19ns                                                     | 4mA  |

#### ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE<br>$V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|----------------------------------------------------------------------------------|

| Plastic DIP | N7433N, N74LS33N                                                                 |

NOTE:

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

### FUNCTION TABLE

H = HIGH voltage level L = LOW voltage level

| INPUTS |   | OUTPUT |

|--------|---|--------|

| A      | В | Y      |

| L      | L | н      |

| L      | н | L      |

| н      | L | L      |

| н      | н | ι ι    |

#### INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74LS   |

|------|-------------|------|--------|

| A, B | Inputs      | 1ul  | 1LSul  |

| Y    | Output      | 30ui | 10LSul |

|      |             |      |        |

NOTE:

Where a 74 unit load (uI) is understood to be  $40\mu A I_{IH}$  and  $-1.6mA I_{IL}$ , a 74LS unit load (LSuI) is  $20\mu A I_{IH}$  and  $-0.4mA I_{IL}$ .

#### PIN CONFIGURATION

# 7437, LS37, S37 Buffers

Quad Two-Input NAND Buffer Product Specification

Logic Products

| TYPE   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7437   | 11ns                         | 22mA                              |

| 74LS37 | 12ns                         | 3.5mA                             |

| 74S37  | 4ns                          | 33mA                              |

# ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|-------------------------------------------------------------------------------|

| Plastic DIP | N7437N, N74LS37N, N74S37N                                                     |

| Plastic SO  | N74S37D                                                                       |

For information regarding devices processed to Military Specifications, see the Signetics Military Products

| INP | OUTPUT |   |

|-----|--------|---|

| A   | Y      |   |

| L   | L      | н |

| L   | н      | н |

| н   | L      | н |

| н   | н      | L |

H = HIGH voltage level L = LOW voltage level

FUNCTION TABLE

# INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74S   | 74LS   |

|------|-------------|------|-------|--------|

| A, B | Inputs      | 1ul  | 2Sul  | 1LSul  |

| Y    | Output      | 30ul | 30Sul | 30LSul |

NOTE:

Data Manual

Where a 74 unit load (ul) is understood to be 40µA I<sub>IH</sub> and -1.6mA I<sub>IL</sub> a 74S unit load (Sul) is 50µA I<sub>IH</sub> and -2.0mA I<sub>IL</sub>, and 74LS unit load (LSul) is 20µA I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

## PIN CONFIGURATION

# 7438, LS38, S38 Buffers

# Quad Two-Input NAND Buffers (Open Collectors) Product Specification

# Logic Products

| ТҮРЕ   | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL) |

|--------|------------------------------|-----------------------------------|

| 7438   | 13ns                         | 28mA                              |

| 74LS38 | 19ns                         | 3.5mA                             |

| 74S38  | 6.5ns                        | 33mA                              |

# ORDERING CODE

| PACKAGES    | COMMERCIAL RANGE $V_{CC} = 5V \pm 5\%$ ; $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |

|-------------|-------------------------------------------------------------------------------|

| Plastic DIP | N7438N, N74LS38N, N74S38N                                                     |

| Plastic SO  | N74S38D, N74LS38D                                                             |

#### NOTE:

OUTPUT

Y

н

н

н

L

For information regarding devices processed to Military Specifications, see the Signetics Military Products Data Manual.

# INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

| PINS | DESCRIPTION | 74   | 74S   | 74LS   |

|------|-------------|------|-------|--------|

| A, B | Inputs      | 1ul  | 2Sul  | 1LSul  |

| Y    | Output      | 30ul | 30Sul | 30LSul |

#### NOTE:

Where a 74 unit load (ul) is understood to be 40  $\mu$  I<sub>IH</sub> and -1.6mA I<sub>IL</sub>, a 74S unit load (Sui) is 50  $\mu$ A I<sub>IH</sub> and -2.0mA I<sub>IL</sub>, and 74LS unit load (LSui) is 20  $\mu$ A I<sub>IH</sub> and -0.4mA I<sub>IL</sub>.

FUNCTION TABLE

A

L

L

н

н

H = HIGH voltage level L = LOW voltage level

INPUTS

в

L

н

L

н

# 7439 Buffer

Quad Two-Input NAND Buffer (Open Collector) **Product Specification**

Logic Products

| ТҮРЕ | TYPICAL PROPAGATION<br>DELAY | TYPICAL SUPPLY CURRENT<br>(TOTAL)                     |